半導体製造において、成膜とは、材料の薄膜をシリコンウェハー上に形成する基本的なプロセスです。これは付加プロセスであり、マイクロチップの複雑な多層構造を構築することを意味します。これは、材料を除去してパターンを作成する減算プロセスであるエッチングとは対照的です。

成膜は単一の動作ではなく、原子層ごとにチップの層を構築するために使用される高度に制御された技術のカテゴリーです。選択された特定の方法(化学的か物理的か)は、最終的な半導体デバイスの性能、信頼性、およびコストを直接決定する重要なエンジニアリング上の決定です。

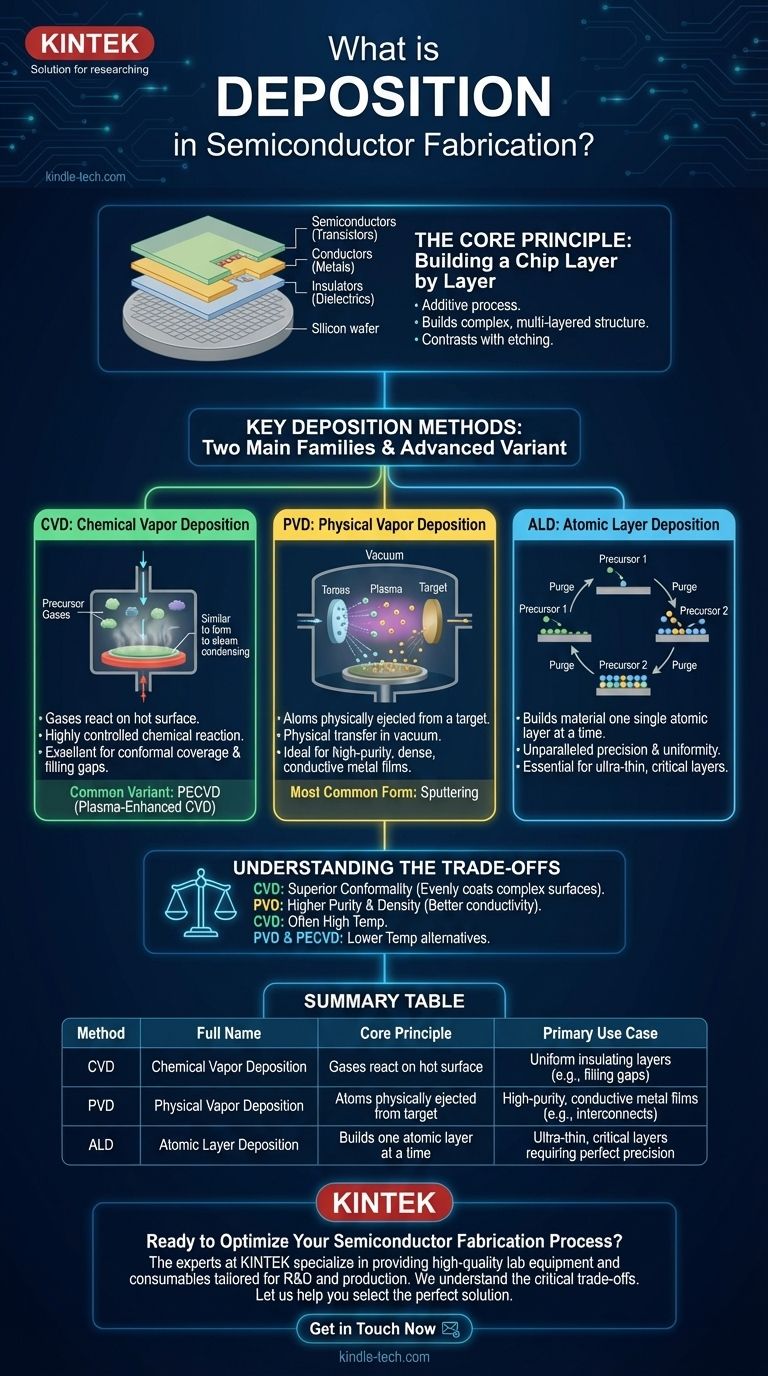

核心原理:チップを層状に構築する

現代のマイクロプロセッサは、何十億ものコンポーネントを持つ信じられないほど複雑な微細な超高層ビルに似ています。成膜は、各フロアとその間の配線を構築するために使用されるプロセスです。

付加プロセス

シリコンウェハーを建物の基礎と考えてください。成膜は、その基礎全体に新しい、完全に均一な材料の層を追加するプロセスです。これは、絶縁層、導電性金属、または別の半導体材料である可能性があります。

成膜された層の目的

成膜された各層は特定の機能を果たします。

- 二酸化ケイ素(SiO₂)のような絶縁体(誘電体)は、異なるコンポーネント間での電流の漏れを防ぎます。

- 銅やアルミニウムのような導体は、チップ内で信号を伝達する「配線」または相互接続を形成します。

- ポリシリコンのような半導体は、すべてのデジタルロジックの基礎となるオン/オフスイッチであるトランジスタ自体を構築するために使用されます。

主要な成膜方法:2つの主要なファミリー

エンジニアは、これらの層を成膜するために2つの主要な技術ファミリーを使用します。それぞれに明確な利点と使用例があります。選択は、成膜される材料と最終デバイスでの役割に完全に依存します。

化学気相成長法(CVD)

CVDでは、ウェハーをチャンバーに入れ、1つまたは複数の揮発性前駆体ガスにさらします。これらのガスは、ウェハーの高温表面で反応または分解し、目的の固体膜を生成します。

これは、蒸気が冷たい窓に水の層として凝縮するのと似ていますが、液体ではなく固体膜を作成する高度に制御された化学反応です。プラズマ強化CVD(PECVD)は、プラズマを使用してこれらの反応を低温で可能にする一般的な変種です。

物理気相成長法(PVD)

PVDでは、成膜される材料は固体ターゲットとして始まります。このターゲットは、真空中で高エネルギーイオン(通常はアルゴンプラズマから)によって衝撃を受け、ターゲットから原子が物理的に剥離されます。

これらの放出された原子は真空を通過し、ウェハーをコーティングします。最も一般的なPVDの形態はスパッタリングであり、これは「砂」(放出された原子)がウェハー上に新しい層を形成するために堆積する、一種の原子スケールのサンドブラストとして視覚化できます。

原子層堆積法(ALD)

最先端のアプリケーションでは、原子層堆積法(ALD)は比類のない精度を提供します。これは、材料を文字通り1つの原子層ずつ構築するCVDプロセスの一種であり、完璧な均一性と膜厚の制御を提供します。

トレードオフを理解する

CVDとPVDの選択は恣意的なものではなく、層の要件に基づいた重要なエンジニアリング上のトレードオフです。

コンフォーマルカバレッジ

CVDプロセスは一般的にコンフォーマリティ、つまり複雑な3次元表面を均一にコーティングする能力に優れています。反応ガスが小さな溝や穴に流れ込んでから反応するため、均一な層が形成され、これは密に詰め込まれた配線間の絶縁に不可欠です。

純度と密度

PVDは、化学プロセスではなく物理的な転送プロセスであるため、金属膜の成膜によく使用されます。これにより、より高い純度と密度の膜が得られ、電気伝導性が向上します。

温度と損傷

従来のCVDプロセスは、化学反応を促進するために非常に高い温度を必要とすることがよくあります。これらの温度は、以前に製造されたチップ上の層を損傷する可能性があります。PVDとPECVDは、はるかに低い温度で動作できるため、貴重な代替手段です。

目標に合った適切な選択をする

成膜方法は常に、チップのアーキテクチャ内の特定の機能を果たすように選択されます。

- 金属配線間の絶縁層の作成が主な焦点である場合:優れたギャップ充填能力と均一なカバレッジを提供するため、CVD(PECVDなど)の形式を使用する可能性が高いです。

- 金属配線(相互接続)の成膜が主な焦点である場合:高純度で高密度、高導電性の膜を作成するために、PVD(スパッタリング)を使用する可能性が高いです。

- トランジスタの超薄型で重要なゲート酸化膜の構築が主な焦点である場合:必要な原子レベルの精度と完璧さを達成するために、原子層堆積法(ALD)を使用する必要があります。

最終的に、成膜を習得することは半導体産業全体にとって不可欠であり、それがチップが構築されるまさにそのプロセスだからです。

要約表:

| 方法 | 正式名称 | 核心原理 | 主な用途 |

|---|---|---|---|

| CVD | 化学気相成長法 | ガスが加熱されたウェハー表面で反応し、固体膜を形成します。 | 均一な絶縁層(例:ギャップ充填)に優れています。 |

| PVD | 物理気相成長法 | 原子がターゲットから物理的に放出され、ウェハーをコーティングします。 | 高純度で導電性の金属膜(例:相互接続)に最適です。 |

| ALD | 原子層堆積法 | CVDの変種で、材料を原子層ごとに構築します。 | 完璧な精度を必要とする超薄型で重要な層に不可欠です。 |

半導体製造プロセスを最適化する準備はできていますか?

適切な成膜技術を選択することは、デバイスの性能と歩留まりにとって非常に重要です。KINTEKの専門家は、半導体R&Dおよび生産の正確なニーズに合わせた高品質の実験装置と消耗品を提供することに特化しています。

CVD、PVD、ALD間の重要なトレードオフを理解しています。絶縁誘電体または高導電性金属相互接続のいずれを成膜する場合でも、お客様の特定のアプリケーションに最適なソリューションを選択するお手伝いをいたします。

当社のソリューションがお客様のラボの能力をどのように向上させ、イノベーションを推進できるかについて話し合うために、今すぐ当社のチームにご連絡ください。

ビジュアルガイド