半導体製造の核心は、純粋なシリコンウェーハ上に何十億もの電子スイッチからなる微細な都市を構築するプロセスです。これは単一の動作ではなく、数百もの異なるステップからなる高度に制御されたシーケンスであり、大きく分けて4つの主要な段階に分けられます。シリコンウェーハの作成、ウェーハ上での回路の製造(フロントエンド)、それらの回路の配線(バックエンド)、そして最後に完成したチップのテストとパッケージングです。各段階は、現代の産業において最も要求の厳しいレベルの精度を必要とします。

理解すべき中心的な概念は、チップ製造が、付加プロセスと除去プロセスを繰り返すサイクルであるということです。時には原子数個分の厚さしかない材料の層が、シリコンウェーハ上に細心の注意を払って堆積され、光を用いてパターン化され、その後選択的にエッチング除去されることで、現代の集積回路を構成する何十億ものトランジスタが徐々に形成されます。

砂からシリコンへ:ウェーハの作成

回路が作られる前に、その基盤は完璧でなければなりません。この基盤は、ほぼ完璧な超高純度のシリコンディスクであり、ウェーハと呼ばれます。

原材料:多結晶シリコン

プロセスは石英砂(二酸化ケイ素)から始まり、これを加熱・精製して冶金グレードのシリコンを製造します。これはさらに精製されて電子グレードの多結晶シリコンとなり、99.9999999%の純度を持つ材料です。この極端な純度は譲れないものであり、わずかな不純物でもチップの電気的特性を損なう可能性があります。

インゴットの成長

この多結晶シリコンはるつぼで溶融されます。小さな種結晶が溶融シリコンに浸され、回転させながらゆっくりと引き上げられます。引き上げられるにつれて、溶融シリコンは冷却・固化し、種結晶の結晶構造に従います。これにより、長さ2メートル以上、重さ数百キログラムにもなる、インゴットまたは「ブール」として知られる大きな単結晶の円柱が生成されます。

スライスと研磨

円柱状のインゴットは、ダイヤモンドチップの鋸を使用して非常に薄いディスクにスライスされます。ウェーハとして知られるこれらの生ディスクは、鏡のような欠陥のない表面になるまで研磨されます。典型的なウェーハは厚さ1ミリメートル未満ですが、完全に平坦でなければなりません。

チップ製造の核心:フロントエンド・オブ・ライン(FEOL)

ここでは、チップの基本的なオン/オフスイッチであるトランジスタが、シリコンウェーハの表面に直接構築されます。これは、4つの主要なプロセスの繰り返しサイクルを通じて行われます。

ステップ1:フォトリソグラフィー(設計図)

フォトリソグラフィーは、チップ製造において最も重要な単一のステップです。フォトレジストと呼ばれる感光性材料の層がウェーハに塗布されます。回路の1層の設計図を含むステンシルのように機能するマスクがウェーハの上に配置されます。その後、特定の波長の光(多くの場合、深紫外光、またはDUV/EUV)がマスクを通して照射され、露光されたフォトレジストの化学構造を変化させます。

ステップ2:エッチング(パターンの彫刻)

次に、ウェーハは軟化したフォトレジストを除去する化学物質またはプラズマにさらされます。これにより、硬化したフォトレジストのパターン層が残り、ウェーハの一部を保護し、他の部分を露出させます。エッチングプロセスでは、ガス(ドライエッチング)または液体(ウェットエッチング)を使用して露出した領域から材料を除去し、下層に回路パターンを彫刻します。

ステップ3:成膜(新しい層の追加)

エッチング後、新しい材料層がウェーハに追加されます。化学気相成長法(CVD)は、ガスが反応してウェーハ上に固体膜を形成するプロセスで、絶縁(誘電体)層の作成に使用されます。物理気相成長法(PVD)、またはスパッタリングは、ターゲット材料にイオンを衝突させ、原子を叩き出してウェーハ上に堆積させるもので、金属層によく使用されます。

ステップ4:ドーピング(導電率の変更)

トランジスタを機能させるには、シリコン自体の電気的特性を変更する必要があります。これはイオン注入によって行われます。これは、高エネルギー粒子加速器が特定のイオン(ホウ素やリンなど)をシリコンウェーハに打ち込むプロセスです。この「ドーピング」により、トランジスタがオン/オフを切り替えることを可能にするN型(負型)およびP型(正型)領域が作成されます。

このリソグラフィー、エッチング、成膜、ドーピングのサイクルが何百回も繰り返され、現代のトランジスタの複雑な3次元構造が構築されます。

トランジスタの接続:バックエンド・オブ・ライン(BEOL)

FEOL段階で何十億ものトランジスタが形成された後、それらを配線する必要があります。相互接続として知られるこの「配線」は、トランジスタの上に構築された銅またはアルミニウムの経路からなる高密度多層グリッドです。

メタライゼーションプロセス

BEOLプロセスはFEOLと密接に似ていますが、トランジスタではなく導電性経路の作成に焦点を当てています。絶縁材料の層が堆積され、その後、リソグラフィーとエッチングを使用して、配線が配置されるトレンチとビア(垂直接続)が作成されます。

配線層の構築

これらのトレンチは、ダマシンと呼ばれるプロセスで銅で埋められます。表面の余分な銅は研磨され、象眼細工の銅配線が施された完全に平坦な層が残ります。このプロセスを繰り返して、個々のトランジスタを機能する回路に接続する10〜20層の配線からなる複雑な「ハイウェイシステム」を構築します。

トレードオフと課題の理解

半導体製造プロセスは、その極端な課題によって特徴付けられます。成功は、それらを克服する能力によって測られます。

清浄度の専制

現代のトランジスタは非常に小さいため、たった1つの塵の粒子が巨大な岩のように回路をショートさせ、チップ全体を破壊する可能性があります。このため、チップはクリーンルームで製造されます。これは、手術室よりも数千倍も清潔な施設です。作業員は汚染を防ぐために頭からつま先まで「バニースーツ」を着用しなければなりません。

より小さなノードの追求

業界の進歩は、トランジスタを小型化することによって推進されており、これはムーアの法則によって説明される傾向です。これらの「プロセスノード」(例:7nm、5nm)は、チップ上の特徴のスケールを指します。特徴が縮小するにつれて、量子トンネル効果(電子が絶縁体を透過する現象)のような物理的な課題が顕著になり、新しい材料やトランジスタ設計(FinFETなど)が必要になります。

歩留まり:成功の究極の指標

歩留まりとは、ウェーハあたりの動作するチップの割合です。プロセスには何百ものステップがあるため、どの段階でのわずかなエラーでも欠陥が生じる可能性があります。90%の歩留まりは高く聞こえるかもしれませんが、それは非常に高価な生産の10%が無価値であることを意味します。歩留まりを1〜2%改善するだけでも、数百万ドルの追加収益につながる可能性があります。

チップの最終化:組み立てとテスト

何百ものステップを経て、ウェーハには何百、何千もの個々のチップ、すなわちダイが保持されています。

ウェーハテストとダイシング

まず、自動プローブがウェーハ上の個々のダイをテストし、機能しているものを特定します。その後、ウェーハはダイシングと呼ばれるプロセスで、ダイヤモンドソーによって個々のダイに切断されます。

パッケージングと最終テスト

機能するダイはその後、パッケージングのために送られます。小さく壊れやすいシリコンダイは基板に搭載され、保護用のプラスチックまたはセラミックのハウジングに封入されます。このパッケージは、チップを外部と接続するための金属ピンまたはパッドを提供します。パッケージング後、チップは出荷前に最終的な厳格なテストを受けます。

このプロセスが重要な理由

チップ製造の基本を理解することは、テクノロジー全体の状況にとって重要な文脈を提供します。

- もしあなたの主な焦点がエンジニアリングや研究であるなら: リソグラフィー、エッチング、成膜、ドーピングの反復サイクルが、すべての現代エレクトロニクスの基本的な構成要素であることを認識してください。

- もしあなたの主な焦点がビジネスや投資であるなら: 歩留まり、製造工場(ファブ)の莫大な設備投資、そしてより小さなプロセスノードへの絶え間ない競争が、市場競争とサプライチェーンダイナミクスの主要な推進要因であることを理解してください。

- もしあなたの主な焦点が一般的なテクノロジーであるなら: あなたの手にあるスマートフォンやクラウドで稼働しているサーバーが、人類がこれまでに開発した中で最も複雑で精密で高価な製造プロセスの一つによって生み出されたものであることを認識してください。

結局のところ、デジタル世界は巧妙なソフトウェアだけでなく、ほとんど想像を絶する規模の応用物理学と製造精度という物理的な基盤の上に構築されています。

要約表:

| 段階 | 主要プロセス | 目的 |

|---|---|---|

| ウェーハ作成 | 結晶成長&研磨 | 超高純度シリコン基盤の作成 |

| フロントエンド(FEOL) | フォトリソグラフィー、エッチング、成膜、ドーピング | 何十億ものトランジスタの構築 |

| バックエンド(BEOL) | メタライゼーション&ダマシンプロセス | 金属層でトランジスタを配線 |

| 組み立て&テスト | ダイシング、パッケージング、最終テスト | 個々のチップを使用可能な状態にする |

半導体研究または生産のためにラボを装備する準備はできていますか? KINTEKは、成膜システム、エッチングツール、ウェーハハンドリングソリューションなど、半導体製造プロセスに不可欠な高精度ラボ機器と消耗品を専門としています。当社の専門知識は、お客様の作業が要求する信頼性と純度を保証します。今すぐ当社のスペシャリストにお問い合わせください。半導体産業におけるお客様のラボの特定のニーズをどのようにサポートできるかご相談ください。

ビジュアルガイド

関連製品

- 光学窓ガラス基板ウェーハ石英プレート JGS1 JGS2 JGS3

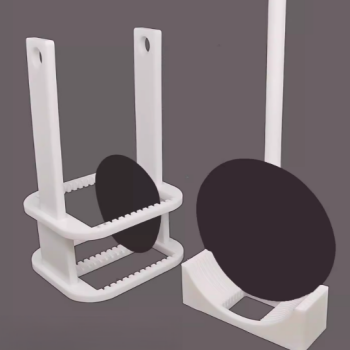

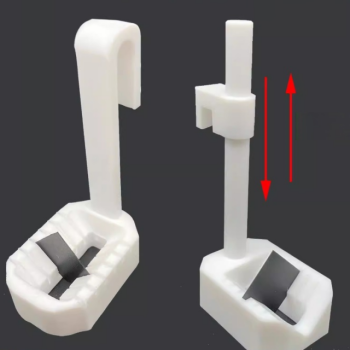

- 半導体およびラボ用途向けのカスタマイズ可能なPTFEウェーハキャリア

- 半導体および医療用ウェーハ加工向けの多用途PTFEソリューション

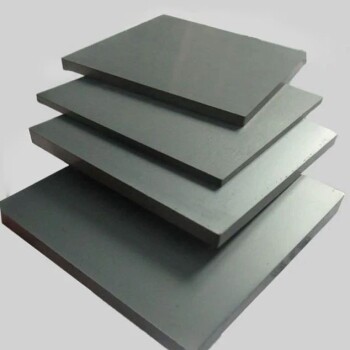

- 炭化ケイ素(SiC)セラミックシート 耐摩耗性エンジニアリング 高性能ファインセラミックス

- ラボおよび半導体処理用のカスタムPTFEウェーハホルダー