半導体製造において、蒸着(エバポレーション)は、材料の薄膜を半導体ウェーハ上に堆積させるために使用される基本的な成膜技術です。このプロセスは、高真空チャンバー内でソース材料を加熱して蒸発させることを含みます。蒸発した原子や分子は移動し、より冷たいウェーハ表面で凝縮し、新しい層を形成します。この方法は物理気相成長(PVD)の一種です。

蒸着は本質的に、真空中で材料を「沸騰」させ、ターゲット基板上に凝縮させるプロセスです。これは薄膜を作成するための直接的でしばしば費用対効果の高い方法ですが、主なトレードオフは、より高度な技術と比較して、膜厚と均一性の精密な制御が難しい点です。

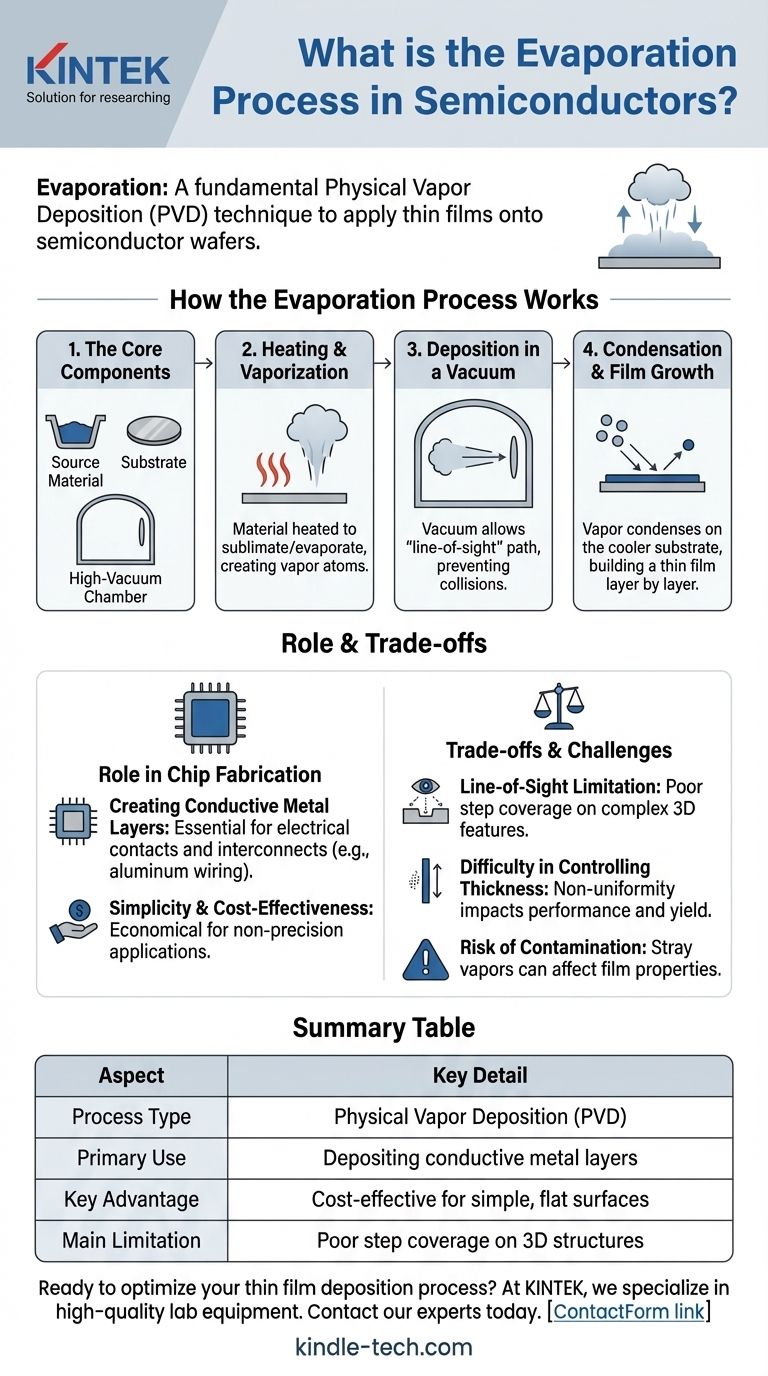

蒸着プロセスの仕組み

その役割を理解するためには、プロセスを主要な機械的ステップに分解すると役立ちます。全体の操作は、特殊で高度に制御された環境内で行われます。

主要な構成要素

システムは主に3つの部分で構成されています。すなわち、ソース材料(例:アルミニウムなどの金属)、コーティングされる基板(半導体ウェーハ)、そしてそれらを囲む高真空チャンバーです。

加熱と蒸発の段階

ソース材料は高温に加熱され、昇華または蒸発し、直接気相に移行します。これにより、蒸発した原子の雲が生成されます。

真空下での成膜

真空は極めて重要です。ほとんどの空気分子を取り除くことで、蒸発したソース原子がソースから基板まで、遮られることなく直線的な経路、すなわち「視線(line-of-sight)」を移動できるようにします。これにより、空気粒子との衝突による散乱や反応を防ぎます。

凝縮と膜の成長

高温の蒸気原子が、はるかに冷たい半導体ウェーハの表面に衝突すると、急速にエネルギーを失い、再び固体状態に凝縮します。このプロセスにより、基板上に固体薄膜が徐々に層をなして形成されます。

チップ製造における蒸着の役割

蒸着は最新のチップ上のすべての層に使用されるわけではありませんが、その特性が適している特定の用途においては依然として貴重なツールです。

導電性金属層の作成

蒸着の主な用途の1つは、金属膜の堆積であり、特に電気接点や相互接続を作成するために使用されます。例えば、チップ全体にわたる様々なトランジスタやコンポーネントを接続するためのアルミニウム配線(「配線」)を形成する一般的な方法です。

シンプルさと費用対効果

より複雑な成膜方法と比較して、熱蒸着の装置とプロセスは比較的シンプルで安価になる可能性があります。これにより、原子レベルの精度を必要としない用途にとって経済的な選択肢となります。

トレードオフと課題の理解

効果的ではありますが、蒸着には明確な限界があり、より要求の厳しいプロセスステップのために他の成膜技術が開発されるきっかけとなりました。

「視線」の制限

材料の蒸気が直線的に移動するため、複雑な三次元表面形状を均一にコーティングするのが困難です。その結果、トレンチの側面では膜が上面よりもはるかに薄くなる、不十分な「ステップカバレッジ」が生じます。

膜厚制御の難しさ

蒸着速度を高い精度で制御することは困難な場合があります。これにより、ウェーハ全体およびウェーハ間で膜厚が不均一になり、デバイスの性能と歩留まりに影響を与える可能性があります。

汚染のリスク

真空チャンバー内の熱くなる可能性のあるコンポーネントは、望ましくない蒸気を放出する可能性があります。これらの迷走分子はソース材料と共堆積し、膜を汚染し、その電気的または物理的特性を変化させ、最終的に品質を低下させる可能性があります。

目標に応じた適切な選択

成膜方法の選択は、作成する膜の技術的要求に完全に依存します。

- 平坦な表面への費用対効果の高い金属コーティングが主な焦点である場合: 蒸着は、単純な接点やボンディングパッドを作成するための非常に適切で経済的な選択肢です。

- 高い均一性で複雑な3D構造をコーティングすることが主な焦点である場合: 視線の制限がなく、優れたステップカバレッジを提供するスパッタリングなどの代替PVD法を検討する必要があります。

- 正確な組成または低汚染の膜の堆積が主な焦点である場合: スパッタリングや化学気相成長(CVD)などのより高度な技術は、これらの重要なパラメータに対してはるかに厳密な制御を提供します。

蒸着の基本的なトレードオフを理解することは、特定の半導体デバイスに適切な製造プロセスを選択するための鍵となります。

要約表:

| 側面 | 主要な詳細 |

|---|---|

| プロセスタイプ | 物理気相成長(PVD) |

| 主な用途 | 導電性金属層の堆積(例:アルミニウム接点) |

| 主な利点 | 単純な平坦面コーティングにおいて費用対効果が高い |

| 主な制限 | 視線成膜による3D構造でのステップカバレッジが不十分 |

薄膜成膜プロセスを最適化する準備はできましたか?

蒸着プロセスは、半導体製造のためのツールの一つにすぎません。適切な装置を選択することは、歩留まりと性能にとって極めて重要です。

KINTEKでは、半導体R&Dおよび製造の正確なニーズを満たすため、成膜システムを含む高品質のラボ機器を専門としています。当社の専門知識は、費用対効果の高い蒸着であれ、複雑な構造のための高度なソリューションであれ、お客様の特定のアプリケーションに最適な技術を選択するのに役立ちます。

プロジェクトの要件について話し合い、ラボに最適なソリューションを見つけましょう。 今すぐ専門家に連絡して、製造能力を向上させましょう。

ビジュアルガイド