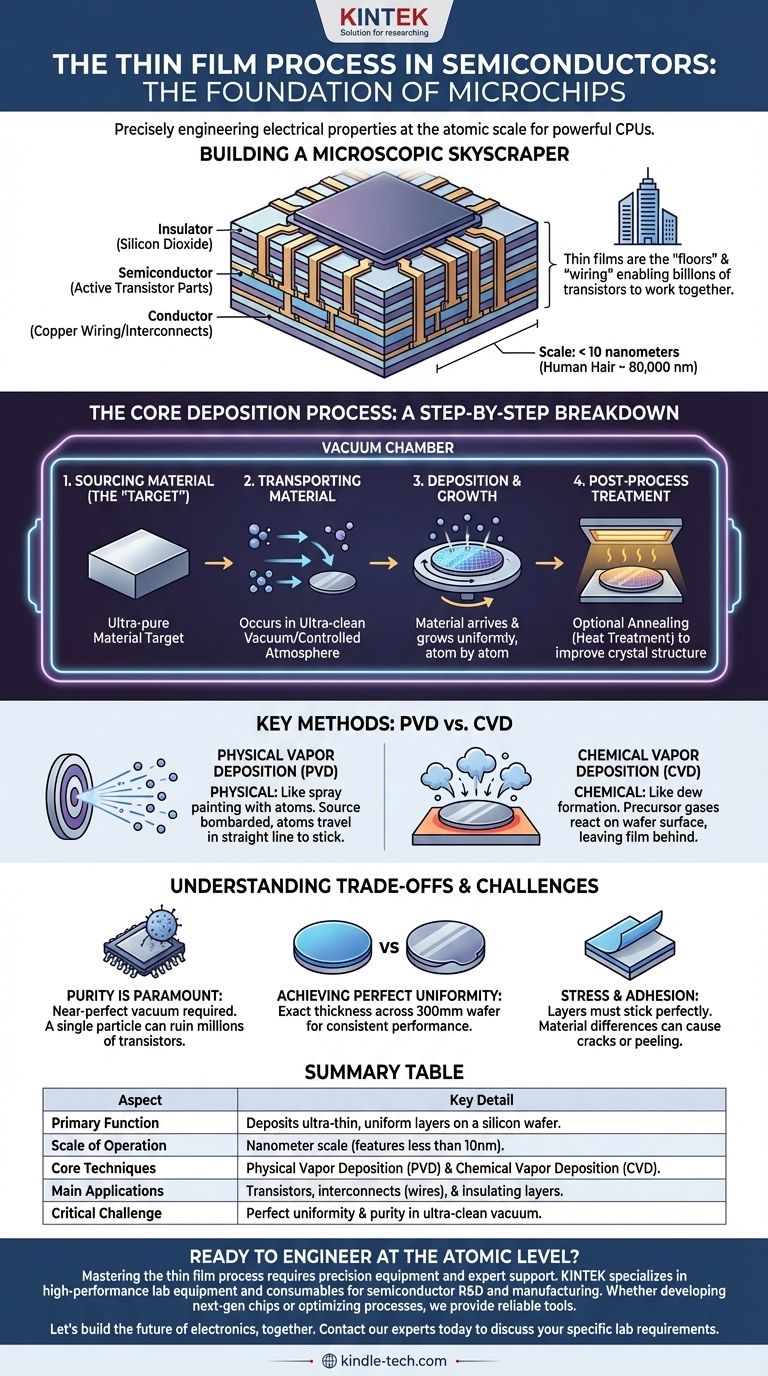

半導体製造において、薄膜プロセスは集積回路をゼロから構築するための基礎的な技術です。これは、材料を(多くの場合、わずか数原子の厚さの)極めて薄く均一な層として基板、通常はシリコンウェーハ上に堆積させる、高度に制御された手法です。このプロセスは、マイクロチップのトランジスタ、配線、その他のコンポーネントを形成する複雑な多層構造を構築するために、異なる材料を用いて数十回繰り返されます。

薄膜プロセスの中核は、単に層を追加することではなく、原子スケールでマイクロチップの電気的特性を正確に設計することにあります。これを習得することが、単なるシリコンの断片と強力な中央処理装置とを分ける違いとなります。

なぜ薄膜が現代エレクトロニクスの礎なのか

微小な超高層ビルの建設

集積回路は平坦な二次元物体ではありません。それは、数十、あるいは数百の層を持つ、微小な超高層ビル群のような高密度な三次元構造物です。

薄膜堆積は、各「フロア」とそれらの間の「配線」(相互接続)を構築するために使用される工法であり、数十億個のトランジスタが協調して動作することを可能にします。

電気的特性の設計

各層の機能は、堆積される材料によって決定されます。銅のような導電性材料の薄膜は配線を形成し、二酸化ケイ素のような絶縁材料は電気的ショートを防ぎます。

特定の半導体材料の層が堆積され、チップのオン/オフスイッチとして機能するトランジスタの能動部分が作成されます。

驚異的な精度のスケール

このプロセスは、理解するのが難しいナノメートルスケールで動作します。人間の髪の毛一本の太さは約80,000ナノメートルです。薄膜を用いて構築される現代のチップの最小加工寸法は10ナノメートル未満になることがあります。

このレベルの精度を達成するには、物理学、化学、材料科学の進歩を必要とする、60年以上にわたる科学的進歩の蓄積が必要でした。

コアとなる堆積プロセス:ステップごとの内訳

ほぼすべての薄膜堆積技術は、汚染を防ぐために超クリーンな真空チャンバー内で行われる同じ基本的なシーケンスに従います。

ステップ1:材料の調達(「ターゲット」)

プロセスは、新しい層を形成する超高純度の材料源から始まります。この源はしばしばターゲットと呼ばれます。

ステップ2:材料の基板への輸送

ターゲット材料からの原子または分子を基板(シリコンウェーハ)に輸送する必要があります。

これは、異なる技術によって異なる主要なステップですが、純度を確保するために常に真空または高度に制御された雰囲気中で行われます。

ステップ3:堆積と成長

輸送された材料がウェーハ表面に到達し、新しい固体層を形成し始めます。この膜は、表面全体にわたって原子ごとに均一に成長します。

ステップ4:後処理

場合によっては、堆積後にウェーハがアニーリング(高温熱処理)などの最終処理を受けます。これにより、膜の結晶構造と電気的特性が改善されることがあります。

主要な堆積方法:PVD 対 CVD

多くの特定の技術がありますが、それらは一般的に物理気相成長法(PVD)と化学気相成長法(CVD)の2つの主要なファミリーに分類されます。

物理気相成長法(PVD)

PVDは物理的なプロセスです。原子個別のスプレー塗装のようなものと考えてください。エネルギー(イオンビームなど)でソース材料が物理的に衝突され、原子が叩き出されます。

これらの原子は真空チャンバー内を直進し、ウェーハに付着して薄膜を形成します。

化学気相成長法(CVD)

CVDは化学的なプロセスです。冷たい表面に露が形成されるのに似ています。目的の原子を含む特殊な前駆体ガスがチャンバーに導入されます。

これらのガスはウェーハの高温表面で反応し、その化学反応の副産物として、固体薄膜が表面に「残されます」。

トレードオフと課題の理解

理論的なプロセスは単純ですが、実際の実装は極めて困難であり、製造技術の最先端を定義しています。

純度が最優先

プロセス全体は、密閉チャンバー内のほぼ完全な真空中で行われる必要があります。単一の微小な塵粒子がウェーハ上に落ちると、数千または数百万のトランジスタを破壊する欠陥を引き起こす可能性があります。

完全な均一性の達成

堆積された膜は、300mmウェーハ全体で全く同じ厚さでなければなりません。わずかな変動でもチップの異なる部分の性能に違いが生じ、故障につながります。

応力と密着性

各新しい層は、その下の層に完全に接着する必要があります。材料特性の違いは物理的な応力を生じさせ、デバイスを破壊する亀裂や剥がれを引き起こす可能性があります。堆積方法の選択は、これらの特性に大きく影響します。

目標に応じた適切な選択

選択される方法は、堆積される材料と最終的なマイクロチップ内でのその目的に完全に依存します。

- 金属化(チップ配線)が主な焦点の場合:PVDは、銅、アルミニウム、チタンなどの純粋な金属を堆積するための、最も直接的で効果的な方法であることがよくあります。

- 高品質の誘電体層または半導体層が主な焦点の場合:CVDは、優れた膜品質、純度、および複雑な3D構造を均一に被覆する能力を提供するため、トランジスタゲートや絶縁層の構築に不可欠です。

- 先進的な研究開発が主な焦点の場合:先進的なバッテリーや光学コーティングなど、次世代デバイス向けに独自の特性を持つ材料を作成するには、新しい堆積技術の探求が鍵となります。

結局のところ、薄膜プロセスを習得することは、機能する物質そのものを原子層ずつ構築する能力を習得することなのです。

要約表:

| 側面 | 主な詳細 |

|---|---|

| 主な機能 | シリコンウェーハ上に超薄く均一な材料層を堆積させる。 |

| 動作スケール | ナノメートルスケール(10nm未満のフィーチャー)。 |

| コア技術 | 物理気相成長法(PVD)および化学気相成長法(CVD)。 |

| 主な用途 | マイクロチップ内のトランジスタ、相互接続(配線)、絶縁層の作成。 |

| 重要な課題 | 超クリーンな真空環境下で完全な均一性と純度を達成すること。 |

原子レベルでの設計に挑戦しますか?

薄膜プロセスを習得するには、精密な装置と専門家のサポートが必要です。KINTEKは、半導体R&Dおよび製造向け高性能ラボ装置と消耗品を専門としています。先進的なPVD/CVD技術を用いた次世代チップの開発であれ、現在の堆積プロセスの最適化であれ、当社は信頼できるツールと専門知識を提供します。

共にエレクトロニクスの未来を築きましょう。当社の専門家へ今すぐお問い合わせ、お客様固有のラボ要件についてご相談ください。

ビジュアルガイド

関連製品

- 薄膜成膜用アルミニウムコーティングセラミック蒸着用ボート

- 薄膜成膜用タングステン蒸着用ボート

- 電子ビーム蒸着コーティング 無酸素銅るつぼおよび蒸着用ボート

- 高温用途向けモリブデン・タングステン・タンタル蒸着用ボート

- ラミネート・加熱用真空熱プレス機