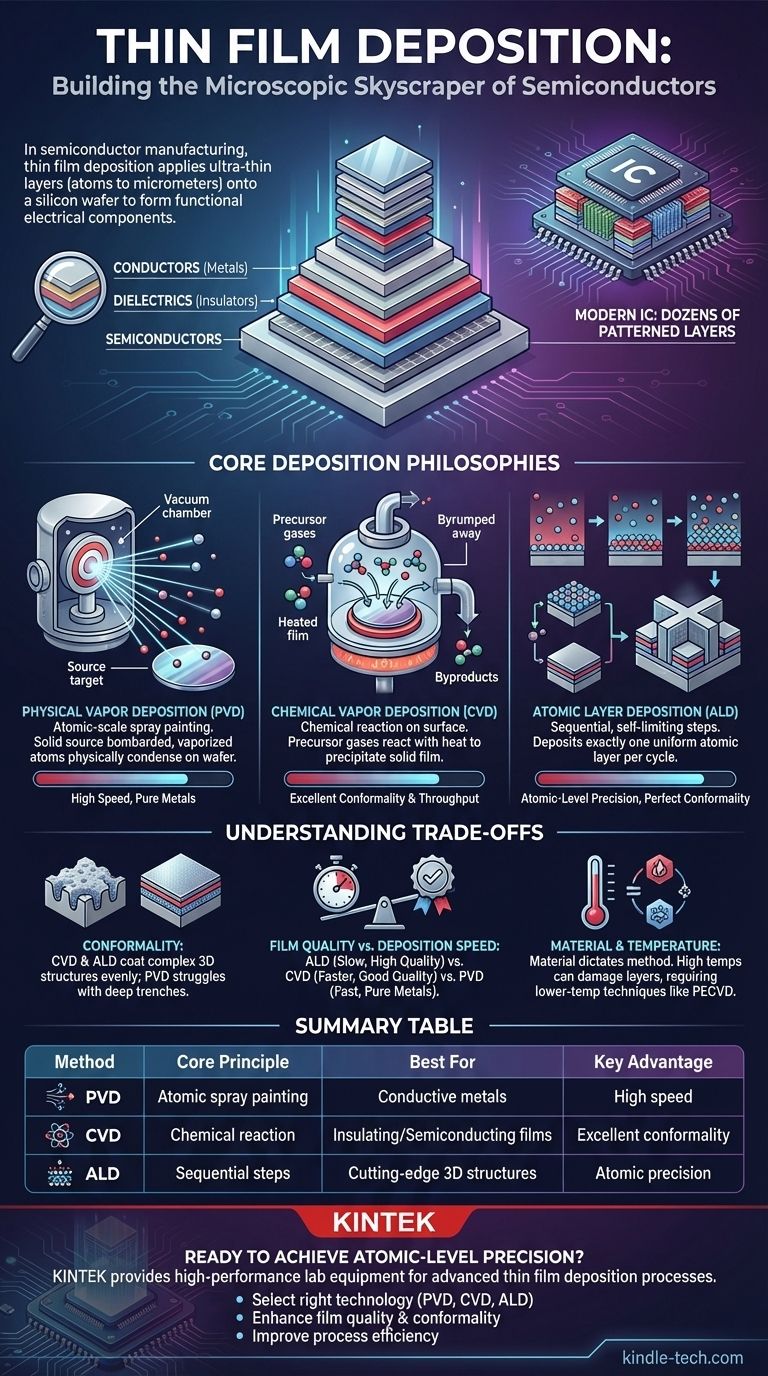

半導体製造において、薄膜堆積とは、シリコンウェーハ上に超薄い材料層を適用するという基礎的なプロセスです。これらの層は、厚さが数原子から数マイクロメートルであることが多く、最新の集積回路を構成するトランジスタや配線などの機能的な電気部品を形成するために、細心の注意を払って積み重ねられます。

薄膜堆積の核心的な目的は、単に表面をコーティングすることではなく、チップの必須である導電層、絶縁層、半導体層を正確に構築することです。堆積方法の選択は、最終的なデバイスの性能、電力効率、信頼性を直接決定する重要なエンジニアリング上の決定となります。

目的:微小な高層ビルの建設

薄膜堆積は、集積回路という微小な多層都市を建設するプロセスです。各層には特定の目的があり、その品質は極めて重要です。

ベアウェーハから複雑な回路へ

完成したチップは単一の物体ではなく、何十ものパターニングされた層の積み重ねです。薄膜堆積は、下の基板または以前の層の上に、これらの層のそれぞれを次々と作成するプロセスです。

電気的特性の変更

半導体製造における主要な目標は、電流の流れを制御することです。堆積は、次の3種類の基本的な層を作成するために使用されます。

- 導体(金属): 信号を異なるコンポーネント間で伝達する配線、つまり「相互接続」を形成します。

- 誘電体(絶縁体): 配線やコンポーネント間での電気の漏洩や短絡を防ぎます。

- 半導体: デジタルロジックの基礎となるオン/オフスイッチであるトランジスタを形成します。

純度と精度の決定的な必要性

ナノスケールでは、誤りの余地はありません。最新のトランジスタの性能は、数個の配置がずれた原子や、堆積された膜のわずかな不純物によって著しく低下する可能性があります。チップのフィーチャーが縮小するにつれて、これらの膜に対する原子レベルの完璧さへの要求はますます厳しくなっています。

主要な堆積の考え方

多くの技術が存在しますが、それらは一般的に物理気相成長法(PVD)と化学気相成長法(CVD)の2つの主要なファミリーに分類されます。

物理気相成長法(PVD)

PVDを原子スケールのスプレー塗装のようなものと考えてください。真空中で固体原料(「ターゲット」)がエネルギーで衝突され、原子が放出されます。これらの気化した原子は直進し、より冷たいウェーハ上に物理的に凝縮して薄膜を形成します。

化学気相成長法(CVD)

CVDはベーキングにより近いです。必要な原子を含む前駆体ガスが、ウェーハのあるチャンバーに導入されます。ウェーハ表面で化学反応(多くの場合、熱によって誘発される)が起こり、目的の原子がガスから「析出」して固体膜を形成します。不要な副生成物は排気されます。

原子層堆積法(ALD)

ALDは、高度に進化したCVDの逐次的な形態です。プロセスを自己制限的なステップに分割し、サイクルごとに正確に1層の均一な原子層を堆積させます。これにより、最先端チップにおける最も複雑な3次元トランジスタ構造を作成するために不可欠な、膜の厚さと均一性に対する比類のない制御が提供されます。

トレードオフの理解

単一の堆積方法がすべての用途に完璧であるわけではありません。エンジニアは、明確な一連のトレードオフに基づいて選択する必要があります。

コンフォーマリティ:複雑な表面形状の被覆

コンフォーマリティは、膜がテクスチャ加工された表面をどれだけうまく覆うかを表します。CVDとALDはコンフォーマリティが高く、複雑な3D構造上に均一な層を堆積できます。PVDは直進的なプロセスであり、深いトレンチの側面や底面を均一にコーティングするのに苦労します。

膜品質 対 堆積速度

一般的に、プロセスの速度が遅いほど、より高品質の膜が得られます。ALDは可能な限り最高の品質と制御を提供しますが、最も遅いです。特定の種類のCVDは、はるかに高速で良好な品質のバランスを提供するため、原子レベルの精度があまり重要でないより厚い膜に適しています。

材料と温度の制約

堆積される材料によって、利用可能な方法が決まります。さらに、堆積温度は大きな懸念事項です。高温は、チップ上の以前に製造された層に損傷を与える可能性があるため、製造フローの後続のステップではプラズマ強化CVD(PECVD)などの低温技術を使用することをエンジニアに強制します。

用途に合わせた方法の選択

堆積技術の選択は、チップアーキテクチャ内での層の機能によって完全に決定されます。

- 導体金属相互接続の作成が主な焦点の場合: PVDは、特に主要な配線レベルにおいて、純粋な金属層を効率的に堆積するための主力となることがよくあります。

- 均一な絶縁膜または半導体膜の堆積が主な焦点の場合: CVDの一種が通常最良の選択であり、膜品質、コンフォーマリティ、スループットの優れたバランスを提供します。

- 最先端の3Dトランジスタゲートや高誘電率誘電体の構築が主な焦点の場合: 原子レベルの精度と、複雑なナノスケールのフィーチャを完全にコーティングできる能力により、ALDは譲れません。

結局のところ、薄膜堆積を習得することは、機能性物質を原子層ずつ構築する技術を習得することなのです。

要約表:

| 方法 | 基本原理 | 最適用途 | 主な利点 |

|---|---|---|---|

| PVD(物理気相成長法) | 真空下での原子スケールのスプレー塗装 | 導体金属相互接続 | 純粋な金属に対する高い堆積速度 |

| CVD(化学気相成長法) | ウェーハ表面での化学反応 | 均一な絶縁膜/半導体膜 | 優れたコンフォーマリティとスループット |

| ALD(原子層堆積法) | 逐次的な自己制限反応 | 最先端の3Dトランジスタゲート | 原子レベルの精度と均一性 |

半導体製造において原子レベルの精度を達成する準備はできましたか?

KINTEKでは、高度な薄膜堆積プロセスに合わせて調整された高性能ラボ機器と消耗品の提供を専門としています。次世代チップを開発する場合でも、現在の生産ラインを最適化する場合でも、当社のソリューションは、お客様の研究が要求する純度、精度、信頼性を保証します。

当社がお手伝いすること:

- お客様の特定の用途に適切な堆積技術(PVD、CVD、ALD)を選択する。

- チップフィーチャーの縮小という課題に対応するため、膜品質とコンフォーマリティを向上させる。

- 信頼性の高い機器と専門家のサポートにより、プロセス効率を向上させる。

さあ、原子層ずつ電子の未来を築きましょう。当社の専門家に今すぐお問い合わせいただき、半導体製造のニーズについてご相談ください!

ビジュアルガイド

関連製品

- 薄膜成膜用アルミニウムコーティングセラミック蒸着用ボート

- 薄膜成膜用タングステン蒸着用ボート

- 電子ビーム蒸着コーティング 無酸素銅るつぼおよび蒸着用ボート

- 高温用途向けモリブデン・タングステン・タンタル蒸着用ボート

- ラミネート・加熱用真空熱プレス機