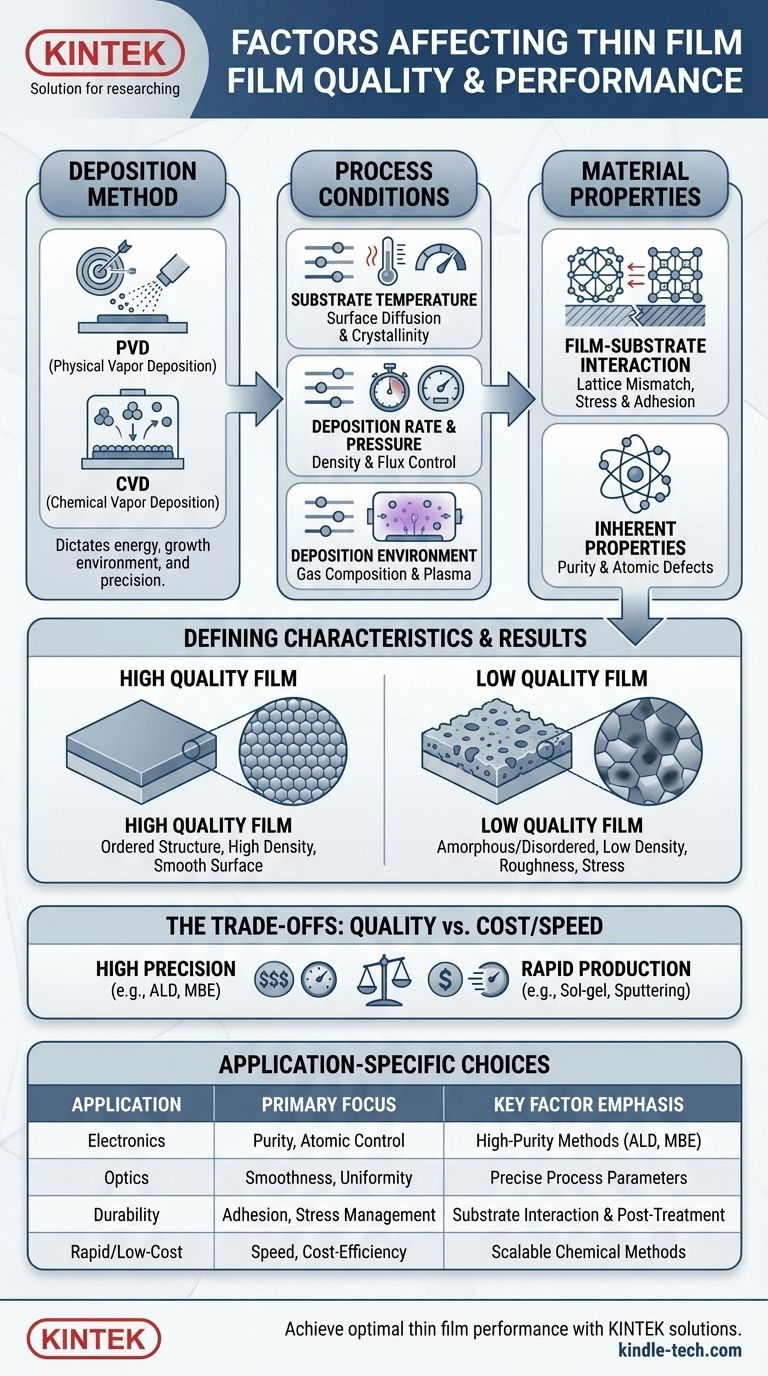

本質的に、薄膜の品質と特性は、選択された成膜法、膜が成長する特定の条件、使用される材料の固有の特性という、3つの主要なカテゴリーの要因によって決定されます。薄膜に依存するデバイスの最終的な性能は、製造プロセス中にこれらの要因がどのように管理および制御されるかの直接的な結果です。

中心的な教訓は、薄膜は単なる材料ではなく、その最終的な特性が成膜プロセス全体の創発的な結果である複雑な構造であるということです。成膜法の選択から基板温度に至るまで、すべての決定が、膜の原子構造、内部応力、そして最終的な性能に直接影響を与えます。

基盤:方法と材料

最初に行う重要な選択は、適切な成膜技術の選択と、膜とそれが成長する表面との相互作用の理解に関係します。これらの決定がプロセス全体の基本的な制約を設定します。

成膜技術の選択

膜の堆積に使用される方法は最も重要な要因です。成膜技術は大きく分けて、物理気相成長法(PVD)と化学気相成長法(CVD)の2つの系統に分類されます。

スパッタリングや真空蒸着などのPVD法は、材料を物理的にソースから基板に移動させます。CVD、原子層堆積(ALD)、ゾル-ゲルなどの化学的方法は、基板表面での化学反応を利用して膜を形成します。この選択が、到達する粒子のエネルギー、成長環境、達成可能な精度を決定します。

基板と膜材料の相互作用

薄膜は孤立して存在するのではなく、基板上に成長します。膜の原子格子と基板の原子格子の不一致は、大きな内部の応力とひずみを生じさせる可能性があります。

この蓄積された張力は、管理されない場合、クラックや、膜が基板から剥がれる剥離(delamination)などの重大な欠陥につながる可能性があります。基板自体の清浄度と表面品質も、極めて重要な初期条件です。

成長の制御:重要な成膜パラメータ

方法が選択されたら、特定のプロセス変数を正確に制御する必要があります。これらのパラメータは、膜の最終的な構造と特性を微調整するためのレバーです。

基板温度

温度は、表面上の原子の移動度を支配する主要な変数です。より高い温度は表面拡散により多くのエネルギーを提供し、原子がより秩序だった結晶構造に落ち着くことを可能にします。温度が不十分だと、より無秩序な、または非晶質の膜になる可能性があります。

成膜速度と圧力

材料が基板に到達する速度(フラックス)と成膜チャンバー内の圧力は重要です。非常に高い成膜速度は、欠陥が解決する前に「埋めて」しまい、低密度の膜につながる可能性があります。チャンバー圧力は、粒子がソースから基板へ移動する方法に影響します。

成膜環境

成膜チャンバー内のガスまたはプラズマの組成は根本的です。CVDでは、前駆体ガスの種類と流量が膜の化学組成を決定します。スパッタリングなどのPVD技術では、プラズマ環境—反応性イオン(ラジカル)の形態とそのエネルギーを含め—が膜の成長と化学に直接影響を与えます。

結果:膜特性の定義

成膜方法とプロセスパラメータの相互作用は、膜の最終的な物理的および機械的特性に現れます。

結晶粒構造と密度

成長中、膜は結晶粒(grains)と呼ばれる微視的な結晶領域を形成します。不規則な結晶粒の成長は「遮蔽効果」を引き起こし、成長中の膜の一部がより高い結晶粒によってブロックされることがあります。これにより空隙と低密度の膜が生じ、その機械的および電気的完全性を損なう可能性があります。

表面粗さと不純物

膜の最終的な平滑性は、成長プロセスの直接的な結果です。表面粗さやその他の不純物は、光学用途では光の散乱を引き起こし、電子機器では電流の流れを妨げる可能性があるため、性能に劇的な影響を与えます。

吸着と脱着のダイナミクス

原子レベルでは、膜の成長は吸着(原子が表面に付着すること)と脱着(原子が表面から離れること)のバランスです。温度と圧力の影響を受けるこれらのプロセスの速度が、膜の純度、密度、および全体的な品質を決定します。

トレードオフの理解:故障モードとコスト

完璧な薄膜を実現するには、一連の妥協を乗り越え、一般的な落とし穴を避ける必要があります。

内部応力とひずみ

前述のように、応力は主要な故障モードです。これは格子不整合だけでなく、膜と基板間の熱膨張率の違いからも生じます。成膜設定の管理と、成膜後の熱処理(アニーリング)の使用が、このリスクを軽減するための主要な戦略です。

純度と原子スケールの欠陥

半導体などの高性能用途では、純度は譲れません。数個の配置が間違った原子や不純物でさえ、マイクロエレクトロニクスデバイスの性能に壊滅的な影響を与える可能性があります。これには、高精度な成膜技術と極めてクリーンな製造条件が必要です。

コスト、速度、精度

膜の品質と製造のコストおよび効率の間には絶え間ないトレードオフがあります。分子線エピタキシー(MBE)やALDのような手法は、比類のない原子レベルの制御を提供しますが、非常に遅く高価です。対照的に、ディップコーティングやスピンコーティングなどの技術は高速で安価ですが、構造的な精度ははるかに低くなります。

用途に合わせた適切な選択

最終的な要因の選択は、薄膜の意図された用途に完全に依存します。

- 高性能エレクトロニクスが主な焦点の場合: 原子レベルの制御を提供するALDやMBEなどの高純度成膜法を優先し、コストと速度の増加を受け入れます。

- 光学コーティングが主な焦点の場合: 表面粗さを最小限に抑え、均一な膜密度を確保するために成膜パラメータを細心の注意を払って制御します。これらは光学特性に直接影響します。

- 機械的耐久性が主な焦点の場合: 内部応力を管理し、クラックや剥離を防ぐために強固な膜-基板密着性を促進することに注力します。

- 迅速または低コストの製造が主な焦点の場合: ゾル-ゲルやスパッタリングなどのスケーラブルな化学的方法を検討し、膜精度の固有のトレードオフを理解し受け入れます。

結局のところ、薄膜技術を習得することは、成膜プロセスと達成する必要のある最終的な膜特性との間の直接的な関係を理解し、制御することにかかっています。

要約表:

| 要因カテゴリー | 主要要素 | 膜への影響 |

|---|---|---|

| 成膜法 | PVD(スパッタリング)、CVD、ALD | 粒子のエネルギー、成長環境、精度を決定する |

| プロセスパラメータ | 基板温度、成膜速度、圧力 | 膜の構造、密度、表面粗さを制御する |

| 材料特性 | 膜-基板の相互作用、格子不整合 | 内部応力、密着性、剥離のリスクに影響を与える |

研究開発の成功に直結する薄膜の最適な性能を実現しましょう。 薄膜の品質は、研究開発の成功に直接影響します。KINTEKは、お客様の成膜ニーズに合わせた高品質なラボ機器と消耗品の提供を専門としています。半導体製造のための精密な制御、光学用途のための均一なコーティング、または機械的用途のための耐久性のある膜が必要な場合でも、当社の専門知識が信頼できる結果をもたらすことを保証します。当社のソリューションが薄膜プロセスを強化し、お客様のイノベーションを推進する方法について、今すぐお問い合わせください。

ビジュアルガイド