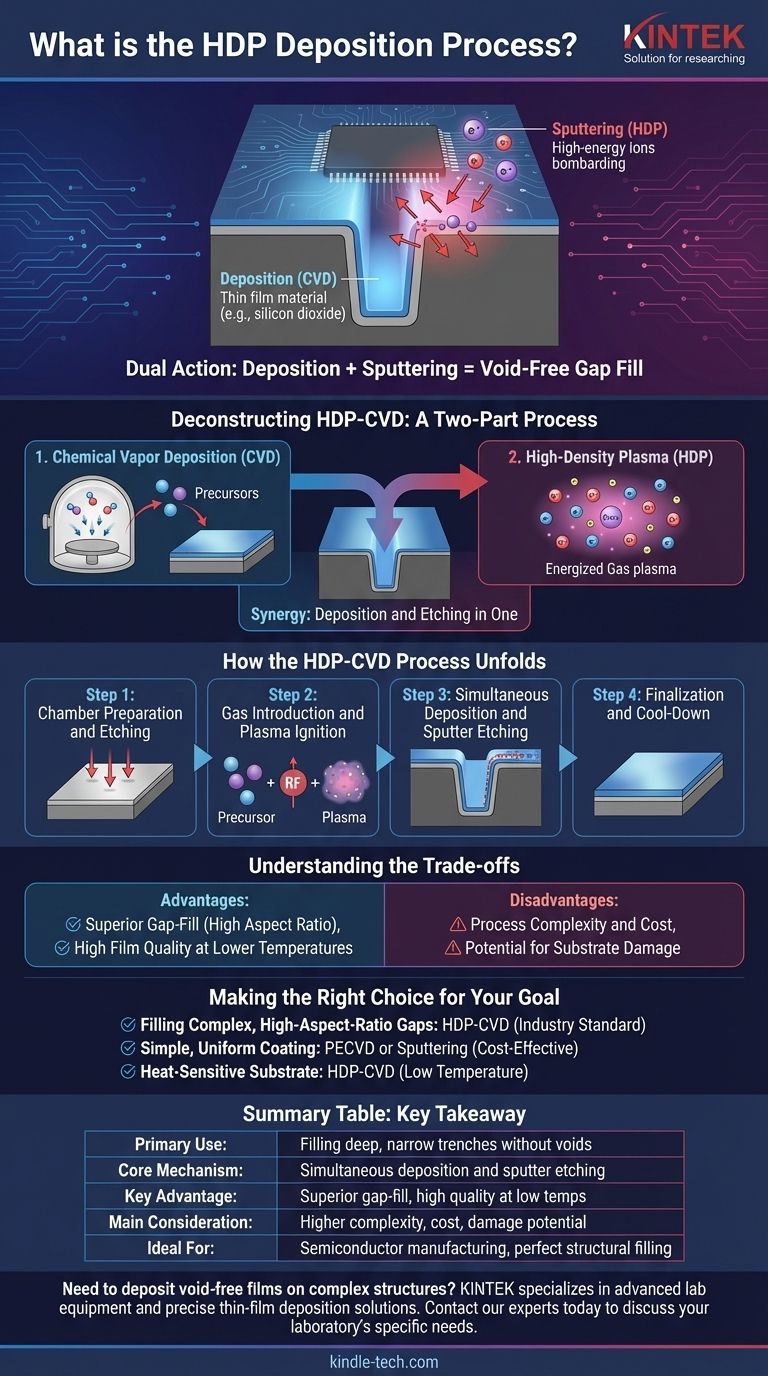

本質的に、高密度プラズマ化学気相成長法(HDP-CVD)は、特にマイクロチップのような複雑な構造内の微細なギャップを埋めるために使用される、高品質な薄膜を堆積させるための高度な製造プロセスです。これは、材料を堆積させると同時にエッチングする活性化された高密度プラズマを使用することで、標準的な化学気相成長法(CVD)を強化し、極めて均一でボイドのない層をもたらします。

標準的な成膜技術が単に表面をコーティングするのに対し、HDP-CVDは材料を追加する行為(成膜)と選択的に除去する行為(スパッタリング)を独自に組み合わせています。この二重の作用が、ボイドや継ぎ目を残さずに深く狭いトレンチを埋める能力の鍵となります。

HDP-CVDの分解:2つのプロセス

HDP-CVDを理解するには、まずその構成要素である成膜方法(CVD)と、それを独自のものにしている強化要素(高密度プラズマ)を理解する必要があります。

基盤:化学気相成長法(CVD)

HDP-CVDの核となるのは、化学気相成長法の一種であるということです。CVDの基本原理は、コンポーネント、すなわち基板を真空チャンバー内に配置することを含みます。

次に、前駆体として知られる特定のガス状化学物質がチャンバー内に導入されます。これらのガスは基板の加熱された表面で反応し、目的の材料の固体薄膜を生成します。

このプロセスには、ガスが表面に輸送される段階から、化学反応、そして最終的な基板上での膜の成長に至るまで、いくつかの明確なステップが含まれます。

強化要素:高密度プラズマ(HDP)

このプロセスを非常に強力にしているのが「HDP」の部分です。プラズマとは、ガスが励起されて原子がイオン化され、イオンと電子の混合物が生成される物質の状態です。

HDP-CVDでは、非常に高密度のプラズマが生成されます。これは、標準的なプラズマベースの成膜方法よりもイオン濃度が大幅に高いことを意味します。この高エネルギーイオンの濃密な雲は、成膜のダイナミクスを根本的に変化させます。

相乗効果:成膜とスパッタエッチングの同時進行

ここに決定的な違いがあります。HDP-CVDでは、2つのプロセスが同時に発生します。

- 成膜: 前駆体ガスが反応し、標準的なCVDと同様に基板上に膜を形成します。

- スパッタリング: プラズマからの高エネルギーイオンが基板を衝突させ、新しく堆積した材料の一部を物理的に叩き落とすか、「スパッタリング」します。

この同時スパッタリングはランダムではありません。これは、特徴部の角やオーバーハングを選択的にエッチングし、成膜材料がボイドの形成を防ぎながら底から深くトレンチを埋めることを可能にします。

HDP-CVDプロセスの展開

典型的なHDP-CVDプロセスは、その独自のギャップ充填能力を達成するために、正確な順序に従います。

ステップ1:チャンバーの準備とエッチング

基板は真空チャンバー内に配置され、非常に低い圧力まで排気されます。基板は目標とするプロセス温度に加熱される場合があります。

多くの場合、膜が完璧に密着するように、イオンを用いた予備的なエッチングステップが実行され、基板表面の汚染物質が除去されます。

ステップ2:ガスの導入とプラズマの着火

前駆体ガスと不活性ガス(アルゴンなど)がチャンバーに導入されます。その後、高周波(RF)エネルギーが印加され、ガスが高密度プラズマに着火されます。

ステップ3:同時成膜とスパッタエッチング

前駆体ガスが表面に材料を堆積させるにつれて、プラズマからの高エネルギーイオンが膜に衝突します。この衝突は傾斜した表面により大きな影響を与え、トレンチの上部の角に蓄積する材料を効果的にスパッタリング除去します。これによりトレンチが開いたままになり、成膜材料が底を埋め続けることができます。

ステップ4:完了と冷却

目的の膜厚に達すると、ガスとRF電源がオフになります。チャンバーは大気圧に戻され、完成した基板が取り出されます。

トレードオフの理解

HDP-CVDは特殊なツールであり、万能の解決策ではありません。その長所と短所を理解することは、適切な適用にとって不可欠です。

利点:優れたギャップ充填能力

これがHDP-CVDを使用する主な理由です。高アスペクト比(深く狭い)のトレンチやギャップをボイドなしで埋める能力は、他のほとんどの成膜技術では比類がありません。

利点:低温での高品質な膜

プラズマによって供給されるエネルギーにより、純粋な熱CVDプロセスと比較して、はるかに低い基板温度で高密度で高品質な膜を形成できます。これにより、高温に耐えられない基板にも適しています。

欠点:プロセスの複雑さとコスト

HDP-CVDに必要な装置は高度で高価です。成膜速度とスパッタエッチング速度の間のデリケートなバランスを維持するには、正確な制御と専門知識が必要です。

欠点:基板損傷の可能性

ギャップ充填を可能にする高エネルギーイオンの衝突は、プロセスが完璧に最適化されていない場合、下にある基板に物理的な損傷を与える可能性もあります。

目標に合わせた適切な選択

成膜方法の選択は、膜の意図された機能と基板のジオメトリに完全に依存します。

- 複雑で高アスペクト比のギャップを埋めることが主な焦点である場合: HDP-CVDは、特に半導体製造において、この正確な課題に対する業界標準のソリューションです。

- 平坦な表面への単純で均一なコーティングが主な焦点である場合: 標準的なプラズマ強化CVD(PECVD)やスパッタリング(PVD技術)のような、より単純な方法の方が効率的で費用対効果が高い可能性があります。

- 熱に敏感な基板への成膜が主な焦点である場合: HDP-CVDは、比較的低温で高品質な膜を生成できるため、優れた選択肢です。

結局のところ、HDP-CVDを選択することは、プロセスの単純さとコストよりも、完璧でボイドのない構造充填を優先するという決定です。

要約表:

| 側面 | 主なポイント |

|---|---|

| 主な用途 | ボイドなしで深い狭いトレンチやギャップ(例:マイクロチップ内)を埋めること。 |

| コアメカニズム | 高密度プラズマによる材料の同時成膜とスパッタエッチング。 |

| 主な利点 | 優れたギャップ充填能力と低温での高品質な膜。 |

| 主な考慮事項 | プロセスの複雑さ、コストの高さ、基板損傷の可能性。 |

| 理想的な用途 | 半導体製造および完璧な構造充填を必要とするアプリケーション。 |

複雑な構造上にボイドフリーの膜を堆積させる必要がありますか?

KINTEKは、精密な薄膜成膜ソリューションを含む高度な実験装置を専門としています。当社の専門知識は、お客様の研究開発を強化するための適切な技術を選択するのに役立ち、最も困難な基板に対しても高品質な結果を保証します。

当社の専門家に今すぐお問い合わせいただき、お客様の研究所の特定のニーズをどのようにサポートできるかをご相談ください。

ビジュアルガイド

関連製品

- 伸線ダイス用ナノダイヤモンドコーティングHFCVD装置

- ラボおよびダイヤモンド成長用のマイクロ波プラズマ化学気相成長MPCVDマシンシステムリアクター

- 915MHz MPCVDダイヤモンドマシン マイクロ波プラズマ化学気相成長装置 リアクター

- 傾斜回転式プラズマ強化化学気相成長(PECVD)装置 管状炉

- 化学気相成長CVD装置システム チャンバースライド式 PECVD管状炉 液体気化器付き PECVDマシン