ウェーハ製造において、成膜とは、シリコンウェーハの表面に材料の薄膜を追加する基本的なプロセスです。金属、絶縁体、または半導体となり得るこれらの層は、トランジスタやその相互接続配線など、集積回路の複雑な三次元構造を構築するために使用される不可欠な構成要素です。

半導体製造の核心は、シリコンウェーハ上に微細な都市を築くために材料を追加したり除去したりするサイクルです。成膜は「建設」段階であり、最終的にチップの機能的な部分となる新しい層を正確に適用するものです。

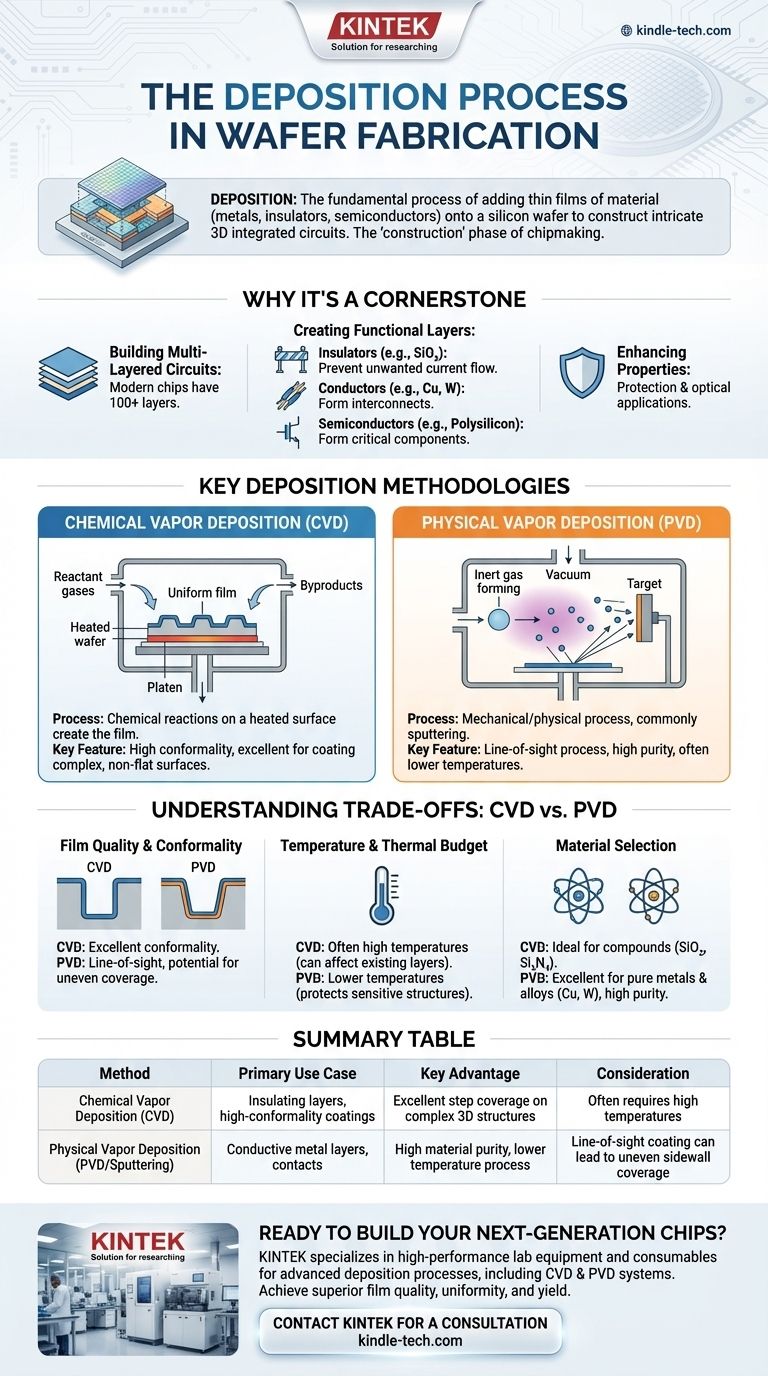

成膜がチップ製造の要である理由

成膜は単にコーティングを追加するだけでなく、特定の予測可能な特性を持つ層を作成するために設計された高度に制御されたエンジニアリングプロセスです。堆積された各膜は、最終デバイスにおいて明確な目的を果たします。

目標:多層回路の構築

現代のマイクロチップは平坦ではありません。それらは信じられないほど複雑な3D構造であり、しばしば100以上の異なる層が積み重ねられています。成膜は、これらの各層を一度に1つずつ構築するために使用されるプロセスです。

導電層と絶縁層の作成

これらの膜の主な機能は、電流の流れを制御することです。

- 二酸化ケイ素などの絶縁体は、電気が流れてはならない場所に電流が流れるのを防ぐために堆積されます。

- 銅やタングステンなどの導体は、チップ上の数百万または数十億のトランジスタを接続する「配線」を形成するために堆積されます。

- ポリシリコンのような半導体は、ゲートなど、トランジスタ自体の重要なコンポーネントを形成するために堆積されます。

基板特性の向上

導電性以外にも、堆積された膜は、その後の製造工程で下層を化学的または物理的な損傷から保護したり、光学用途のために特定の方法で光と相互作用するように特別に設計されたりすることができます。

主要な成膜方法論

目標は常に膜を追加することですが、使用される方法は、堆積される材料と、その純度や均一性など、膜に要求される特性に大きく依存します。主要な2つの技術は、化学気相成長法と物理気相成長法です。

化学気相成長法(CVD)

CVDは、化学反応を利用して膜を形成するプロセスです。反応ガスがウェーハを含むチャンバーに導入されます。これらのガスは加熱されたウェーハ表面に吸着し、反応して固体膜を形成し、その後、チャンバーから除去されるガス状副生成物を放出します。

このプロセスは、ウェーハ上の複雑な非平坦な表面に完全に適合する、非常に均一な膜を作成するのに優れています。これは高いコンフォーマリティとして知られる特性です。

物理気相成長法(PVD)

対照的に、PVDは機械的または物理的なプロセスです。最も一般的な形態はスパッタリングです。

- 汚染物質を除去するためにチャンバーを高真空にします。

- アルゴンなどの不活性ガスが導入され、プラズマが生成されます。

- このプラズマは、堆積される材料で作られた「ターゲット」を衝撃するために使用されます。

- 衝撃により、ターゲットから原子が物理的に叩き出され、それが移動してウェーハをコーティングし、薄膜を形成します。

PVDは、スパッタされた原子がターゲットからウェーハまで比較的直線的に移動するため、スプレー塗装に似た「見通し線」プロセスとしてしばしば説明されます。

トレードオフの理解:CVD vs. PVD

CVDとPVDの選択には、構築される特定の層に関連する重要なトレードオフが伴います。単一の「最良」の方法はなく、選択は特定のステップのエンジニアリング要件によって決定されます。

膜の品質とコンフォーマリティ

CVDは、反応ガスが深いトレンチや複雑な形状に拡散して反応できるため、複雑な地形をコーティングするのに優れています。PVDの見通し線特性は、トレンチの側壁に薄いコーティングを、上部に厚いコーティングをもたらす可能性があり、これは問題となる場合があります。

温度と熱バジェット

CVDプロセスは、必要な化学反応を促進するために高温を必要とすることがよくあります。これは、熱がウェーハ上にすでに製造されている層を損傷または変更する可能性があるため、重大な制約となる可能性があります。多くのPVDプロセスははるかに低い温度で動作できるため、既存の構造の完全性を保護します。

材料の選択

堆積される材料は主要な要因です。CVDは、二酸化ケイ素(SiO₂)や窒化ケイ素(Si₃N₄)などの化合物材料に最適です。PVD、特にスパッタリングは、純粋な金属や合金を堆積するのに非常に効果的であり、膜の純度を優れた制御で提供します。

これを目標に適用する方法

成膜技術の選択は、作成する膜層の特定の要件に基づいた戦略的な決定です。

- 複雑な地形上に均一な絶縁層を作成することが主な焦点である場合:CVDは、その優れたコンフォーマリティにより、どこでも均一なカバレッジを確保するため、しばしば優れた選択肢となります。

- 配線やコンタクト用に純粋な金属膜を堆積することが主な焦点である場合:PVD/スパッタリングは、温度に敏感なデバイス構造とより互換性のあるプロセスで、高い純度と正確な制御を提供します。

- 既存の層を保護するために熱バジェットを管理することが主な焦点である場合:PVDの低温特性は、高温CVDプロセスよりも重要な利点となる可能性があります。

最終的に、成膜は多用途で不可欠なツールであり、チップメーカーがすべての現代エレクトロニクスを動かす基盤となる層を正確に構築することを可能にします。

要約表:

| 成膜方法 | 主な用途 | 主な利点 | 考慮事項 |

|---|---|---|---|

| 化学気相成長法(CVD) | 絶縁層(例:SiO₂)、高コンフォーマリティコーティング | 複雑な3D構造に対する優れた段差被覆性 | しばしば高温を必要とする |

| 物理気相成長法(PVD/スパッタリング) | 導電性金属層(例:Cu、W)、コンタクト | 高い材料純度、低温プロセス | 見通し線コーティングにより、側壁の被覆が不均一になる可能性がある |

次世代チップの構築準備はできていますか?

薄膜の正確な適用は、半導体製造の成功に不可欠です。KINTEKは、CVDおよびPVDシステムを含む、高度な成膜プロセス用の高性能実験装置と消耗品の提供を専門としています。

当社は、お客様のラボパートナーが優れた膜品質、均一性、および歩留まりを達成できるよう支援します。今すぐお問い合わせください。当社のソリューションがお客様の特定のウェーハ製造ニーズをどのように満たせるかについてご相談ください。

ビジュアルガイド

関連製品

- 化学気相成長CVD装置システム チャンバースライド式 PECVD管状炉 液体気化器付き PECVDマシン

- 915MHz MPCVDダイヤモンドマシン マイクロ波プラズマ化学気相成長装置 リアクター

- 真空ステーション付き分割チャンバーCVDチューブ炉 化学蒸着システム装置

- 顧客メイド多用途CVDチューブ炉 化学気相成長チャンバーシステム装置

- RF PECVDシステム RFプラズマエッチング装置