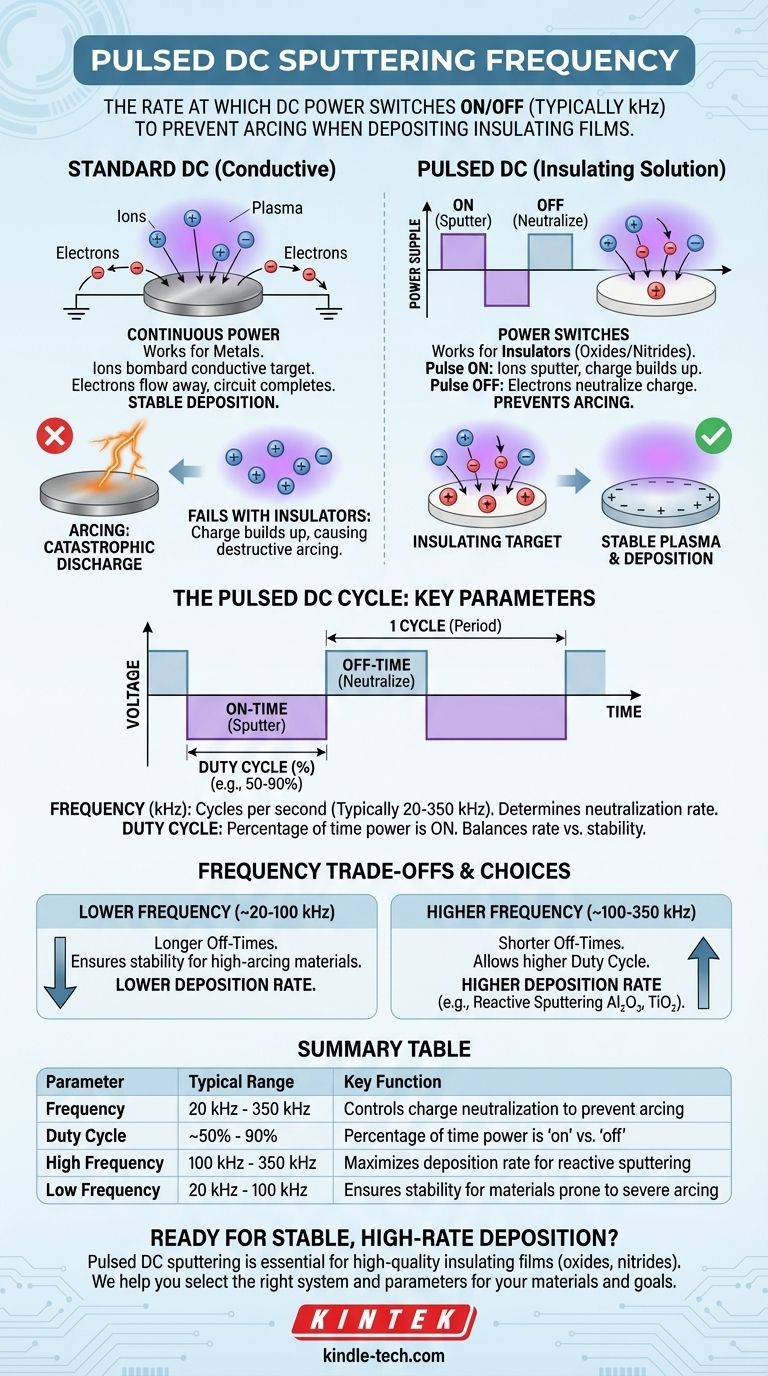

簡単に言えば、パルスDCスパッタリング周波数とは、成膜プロセス中にDC電源がオン・オフを切り替える速度のことで、通常はキロヘルツ(kHz)で測定されます。この技術は、標準的なDCスパッタリングの重要な進化であり、アーク放電と呼ばれる現象のために単純なDCスパッタリングでは効果のない、絶縁性または半絶縁性薄膜を成膜するために特別に設計されています。このパルスの周波数は、プラズマの安定性と膜の成膜速度の両方を制御する重要なパラメータです。

絶縁材料のスパッタリングにおける根本的な問題は、ターゲット表面に正電荷が蓄積され、アーク放電として知られる制御不能な放電を引き起こすことです。パルスDCスパッタリングは、電圧を周期的に中断することでこの問題を解決し、プラズマからの電子がアーク放電が発生する前にこの電荷蓄積を中和する時間を与えます。周波数は、この中和がどれくらいの頻度で発生するかを決定します。

根本的な問題:標準DCが失敗する理由

標準DCスパッタリングは、堅牢で高速なプロセスですが、金属のような電気伝導性材料にのみ適用されます。その物理的特性は、絶縁体を取り扱う際に固有の限界を生み出します。

導電性ターゲットの役割

標準DCスパッタリングでは、導電性金属ターゲットに高い負のDC電圧が印加されます。プラズマからの正イオン(アルゴンなど)がこのターゲットに加速され、材料をスパッタリングします。

ターゲットは導電性であるため、電気回路を完成させ、正イオン電荷の継続的な流入を放散させることができ、プロセスをスムーズかつ無期限に実行できます。

絶縁性ターゲットのジレンマ

酸化物や窒化物のような絶縁性(誘電体)材料をスパッタリングしようとすると、このプロセスは破綻します。正イオンは依然としてターゲットを衝撃しますが、今度はその表面に閉じ込められます。

ターゲット表面へのこの正電荷の蓄積は、しばしば「ターゲット汚染」または「チャージング」と呼ばれます。絶縁体は、その定義上、この電荷を導電できません。

結果:アーク放電

この正電荷の島が成長するにつれて、局所的な電界は信じられないほど強くなります。最終的には、壊滅的な破壊、つまりアーク放電として知られる激しい高電流放電を引き起こすのに十分な強度になります。

アーク放電は非常に破壊的です。ターゲットを損傷したり、基板に大きな微粒子を吹き付けたり(膜を台無しにする)、プラズマを不安定にしたり、完全に消滅させたりして、成膜プロセスを完全に停止させる可能性があります。

パルスDCスパッタリング:設計されたソリューション

パルスDCは、アーク放電の問題を克服するために特別に開発されました。連続的なDC信号を、注意深く制御された一連のパルスに変更します。

コアメカニズム:オン時間とオフ時間

パルスDCサイクルは2つのフェーズで構成されます。

- パルスオン時間:このフェーズ(通常はマイクロ秒単位)では、負電圧が印加され、標準DCプロセスと同様にスパッタリングが発生します。ターゲット上に正電荷が蓄積し始めます。

- パルスオフ時間(または反転):その後、電圧はオフになるか、より高度なシステムでは、短時間、わずかな正電位に反転されます。この短い中断により、プラズマ内の移動性の高い電子がターゲット表面に流れ込み、蓄積された正電荷を中和することができます。

このサイクルは1秒間に数千回繰り返され、電荷がアーク放電を引き起こすほど蓄積するのを防ぎます。

周波数とデューティサイクルの定義

このプロセスを制御する2つのパラメータは次のとおりです。

- 周波数:これは1秒あたりの完全なオン/オフサイクルの数であり、通常は20 kHzから350 kHzの範囲です。これは、電荷中和ステップがどれくらいの頻度で発生するかを決定します。

- デューティサイクル:これは、1サイクル内で電圧が「オン」になっている時間の割合です。90%のデューティサイクルは、サイクル時間の90%がオンで、10%がオフであることを意味します。

周波数とデューティサイクルは、ターゲットを中和するための重要なウィンドウである反転時間の長さを決定します。

トレードオフの理解

周波数の選択は恣意的ではありません。成膜速度とプロセス安定性のバランスを取る必要があります。パルスDCは強力なソリューションですが、絶縁体を成膜するためのもう1つの主要な方法であるRFスパッタリングと比較されることがよくあります。

高周波数(〜100-350 kHz)

高周波数は、アーク放電を防ぎながら、より短い「オフ時間」を可能にします。これは、より高いデューティサイクル(スパッタリングに費やす時間が長くなる)を可能にし、結果としてより高い成膜速度をもたらすため、有利です。Al₂O₃やTiNのような化合物のほとんどの最新の反応性スパッタリングプロセスは、高周波パルスDCを使用しています。

低周波数(〜20-100 kHz)

低周波数は、深刻なアーク放電を起こしにくい材料や、古い電源設計で使用される場合があります。通常、完全な電荷中和を確実にするために、より低いデューティサイクル(より長い「オフ時間」)が必要となり、結果として全体的な成膜速度が低下します。

パルスDC vs. RFスパッタリング

RF(高周波)スパッタリングは、電圧を急速に交互に切り替えること(通常13.56 MHz)でチャージングを回避します。すべての材料に効果的ですが、反応性スパッタリングされた化合物の成膜速度は、最新の高周波パルスDCシステムで達成できる速度よりも著しく低いことがよくあります。ただし、RFは、高絶縁性ソースターゲットから直接スパッタリングする場合(例:石英ターゲットのスパッタリング)のゴールドスタンダードであり続けています。

目標に合った適切な選択をする

適切なスパッタリングパラメータの選択は、材料と性能目標に完全に依存します。

- 反応性スパッタリング(例:Al₂O₃、TiO₂、Si₃N₄の形成)の成膜速度を最大化することが主な焦点である場合:高周波数(100-350 kHz)のパルスDC電源を使用してください。これにより、高速な膜成長のために高いデューティサイクルを実行しながら、アーク放電を効果的に抑制できます。

- 半絶縁性化合物で深刻なアーク放電が発生している場合:中程度の周波数(例:50-100 kHz)と控えめなデューティサイクル(例:80%)から始めて安定したプロセスを確立し、その後、速度を最適化するために両方を徐々に増やしてください。

- 化合物膜の技術を選択する場合:反応性プロセスでの高い成膜速度のためにパルスDCを優先しますが、バルク絶縁ターゲット材料から直接スパッタリングする必要がある場合はRFスパッタリングを選択してください。

最終的に、周波数は、絶縁膜の安定した高品質な成膜に不可欠な電荷中和を正確に制御できるダイヤルです。

要約表:

| パラメータ | 典型的な範囲 | 主な機能 |

|---|---|---|

| 周波数 | 20 kHz - 350 kHz | アーク放電を防ぐための電荷中和速度を制御 |

| デューティサイクル | ~50% - 90% | 電源が「オン」になっている時間の「オフ」に対する割合 |

| 高周波数 | 100 kHz - 350 kHz | 反応性スパッタリングの成膜速度を最大化 |

| 低周波数 | 20 kHz - 100 kHz | 深刻なアーク放電を起こしやすい材料の安定性を確保 |

絶縁膜の安定した高速成膜を実現する準備はできていますか?

パルスDCスパッタリングは、破壊的なアーク放電なしに、高品質の酸化物、窒化物、およびその他の化合物膜を成膜するために不可欠です。KINTEKの専門家は、薄膜プロセスを最適化するための適切な実験装置と消耗品の提供を専門としています。

お客様の特定の材料と成膜目標に最適なスパッタリングシステムとパラメータの選択をお手伝いいたします。

今すぐKINTEKにお問い合わせください お客様のプロジェクトについて話し合い、当社のソリューションがお客様のラボの能力をどのように向上させることができるかを発見してください。

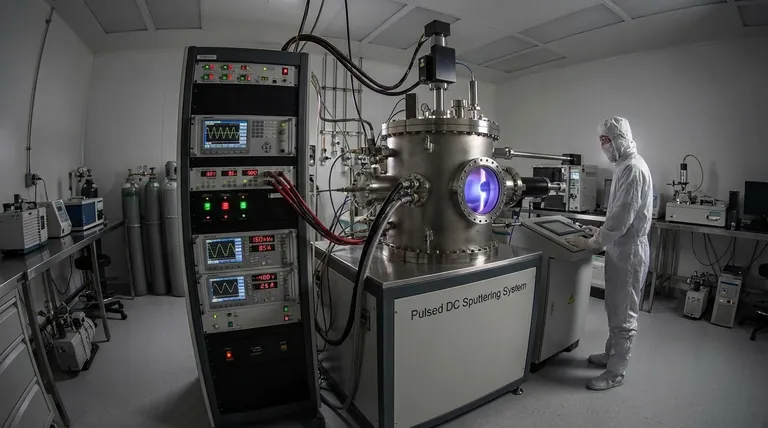

ビジュアルガイド