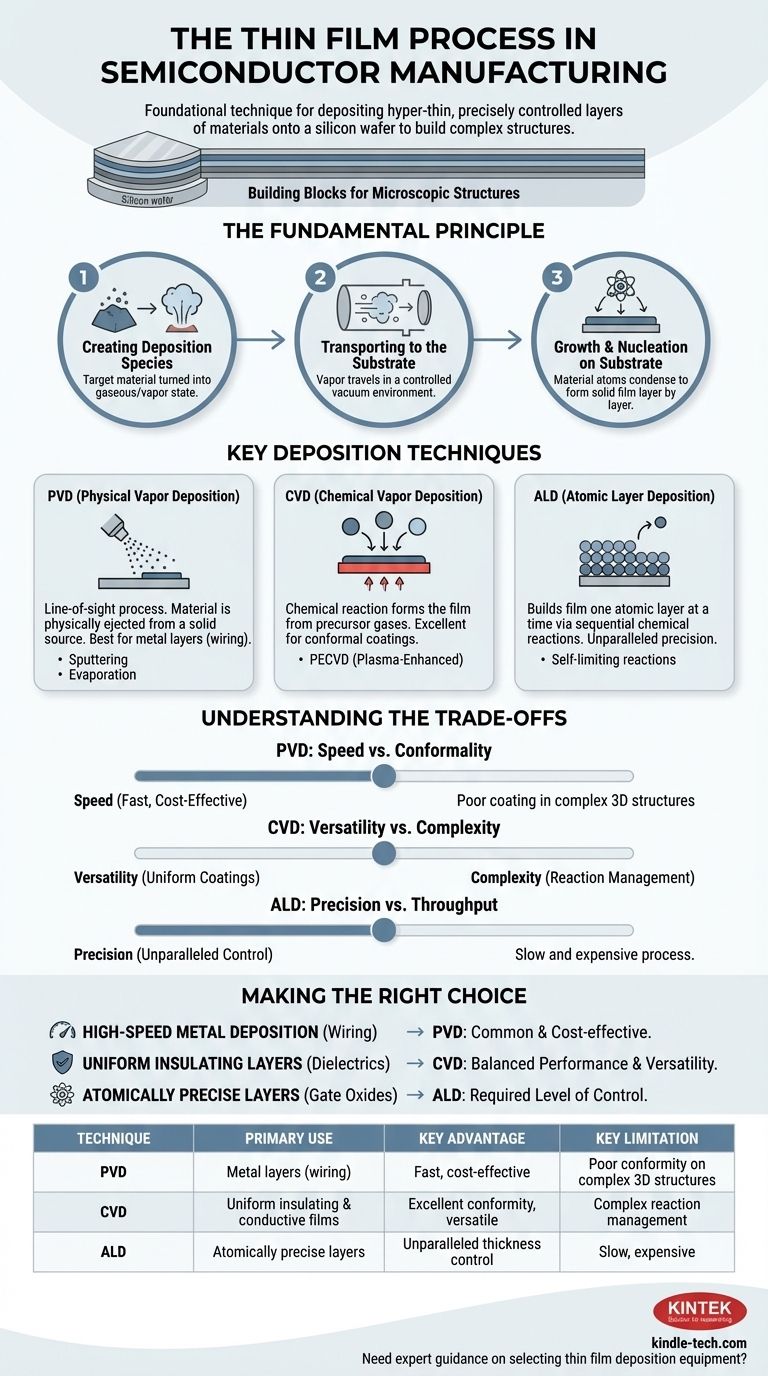

要するに、薄膜プロセスとは、半導体製造の基礎となる技術であり、様々な材料の超薄膜をシリコンウェーハ上に精密に制御しながら堆積させることです。これは単一の方法ではなく、トランジスタや集積回路を形成する複雑な多層構造を体系的に構築するための洗練された一連の技術です。プロセス全体は、絶対的な純度と精度を確保するために、真空または制御された環境下で行われます。

半導体製造における中心的な課題は、微細な三次元構造を構築することです。薄膜堆積は、材料を一度に一層ずつ追加することで不可欠な「ビルディングブロック」を提供し、使用する技術(主にPVD、CVD、またはALD)は、その特定の層に要求される精度、材料、コストによって決定されます。

薄膜成長の基本原理

特定の技術を検討する前に、すべての薄膜堆積が同じ3段階の原理に従っていることを理解することが重要です。この普遍的なプロセスは、最新のチップ上のすべての層を作成するための基盤となります。

ステップ1:堆積種の生成

プロセスは、目的の材料を気体または蒸気状態で生成することから始まります。この「ターゲット材料」は、蒸発またはスパッタリングによって固体源から放出されるか、反応性前駆体ガスとして導入される場合があります。

ステップ2:基板への輸送

材料が蒸気状態になったら、シリコンウェーハ(基板)の表面に輸送されなければなりません。これは、望ましくない粒子や大気ガスによる汚染を防ぐために、高度に制御された真空チャンバー内で行われます。

ステップ3:基板上での成長と核生成

材料の原子や分子がウェーハ表面に到達すると、凝縮して固体膜を形成し始めます。核生成として知られるこの成長プロセスにより、目的の厚さに達するまで材料層が積み重ねられます。

主要な堆積技術の解説

基本原理は同じですが、材料の生成と輸送に使用される方法が特定の技術を定義します。半導体製造において最も重要な3つの方法は、物理気相成長法(PVD)、化学気相成長法(CVD)、および原子層堆積法(ALD)です。

物理気相成長法(PVD)

PVDは「直線的」なプロセスです。原子スケールのスプレー塗装技術だと考えてください。

材料は固体源(ターゲット)から物理的に放出され、直線的に移動してウェーハをコーティングします。これは通常、ターゲットをイオンで衝突させるスパッタリング、またはターゲットを加熱して蒸発させる蒸着によって行われます。

化学気相成長法(CVD)

CVDは化学反応を利用して膜を形成します。1つまたは複数の反応性前駆体ガスが、ウェーハを含むチャンバーに導入されます。

これらのガスが加熱されたウェーハ表面に到達すると反応して分解し、目的の材料の固体膜を残します。一般的なバリエーションとして、より低温で反応を促進するためにプラズマを使用するプラズマ強化CVD(PECVD)があります。

原子層堆積法(ALD)

ALDは利用可能な最も精密な方法であり、文字通り一度に原子一層ずつ膜を構築します。

このプロセスは、自己制限的な一連の化学反応を利用します。前駆体ガスがチャンバーにパルス状に導入され、表面全体が正確に1層の分子でコーティングされます。余分なものはパージされ、2番目のガスが導入されて最初の層と反応し、原子膜が完成します。このサイクルは何百回、何千回と繰り返されます。

トレードオフの理解

単一の堆積方法がすべての用途に最適であるわけではありません。エンジニアは、速度、精度、コストの明確なトレードオフに基づいて、その仕事に最適なツールを選択します。

PVD:速度 対 均一性(コンフォーマリティ)

PVDはしばしば高速で比較的安価であるため、配線(インターコネクト)用の金属層の堆積に最適です。しかし、直線的なプロセスであるため、深く狭いトレンチやその他の複雑な3D構造の内部を均一にコーティングするのは困難です。

CVD:汎用性 対 複雑性

CVDは非常に汎用性が高く、複雑な地形に対して均一な「コンフォーマル」コーティングを作成するのに優れています。これは、多くの異なる誘電体(絶縁体)膜や導電性膜に使用されます。主なトレードオフは、最終膜の不純物を避けるために化学反応を管理する複雑さです。

ALD:精度 対 スループット

ALDは膜の厚さと均一性に対する比類のない制御を提供し、最先端のトランジスタの超薄ゲート酸化膜やその他の重要な層を作成するために不可欠です。主な欠点は、プロセスが非常に遅く高価であるため、絶対的な精度が譲れない層にのみ使用されることです。

アプリケーションに最適な選択をする

薄膜プロセスの選択は、半導体デバイス内の特定の層の目標によって完全に決定される重要なエンジニアリング上の決定です。

- 配線用の高速金属堆積が主な焦点である場合: PVDが最も一般的で費用対効果の高い選択肢です。

- 高品質で均一な絶縁層の作成が主な焦点である場合: CVDとそのバリアント(PECVDなど)が、性能と汎用性の最良のバランスを提供します。

- 最先端のトランジスタ用に原子レベルで正確な層を構築することが主な焦点である場合: ALDのみが要求される制御レベルを提供します。

結局のところ、これらの堆積技術の相互作用を習得することが、現代のエレクトロニクスの絶え間ない進歩を可能にしているのです。

要約表:

| 技術 | 主な用途 | 主な利点 | 主な制限 |

|---|---|---|---|

| PVD(物理気相成長法) | 配線用金属層(インターコネクト) | 高速、費用対効果が高い | 複雑な3D構造に対する均一性の低さ |

| CVD(化学気相成長法) | 均一な絶縁膜および導電膜 | 優れた均一性、汎用性が高い | 複雑な反応管理 |

| ALD(原子層堆積法) | 原子レベルで正確な層(例:ゲート酸化膜) | 比類のない厚さ制御と均一性 | 遅い、高価 |

半導体ラボ用の適切な薄膜堆積装置の選択について専門家のガイダンスが必要ですか? KINTEKは、高精度ラボ機器と消耗品の専門家であり、お客様固有のPVD、CVD、またはALDの要件に合わせたソリューションを提供します。当社の専門知識により、最先端の半導体製造において最適な層の均一性、純度、および性能を達成できます。当社の専門家に今すぐ連絡して、お客様のラボの高度な製造ニーズをどのようにサポートできるかご相談ください!

ビジュアルガイド

関連製品

- 半導体および医療用ウェーハ加工向けの多用途PTFEソリューション

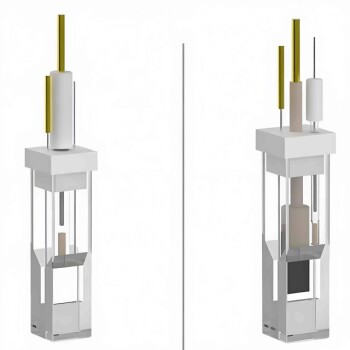

- ラミネート・加熱用真空熱プレス機

- ラボおよび半導体処理用のカスタムPTFEウェーハホルダー

- 半導体およびラボ用途向けのカスタマイズ可能なPTFEウェーハキャリア

- 薄層分光電気分解セル