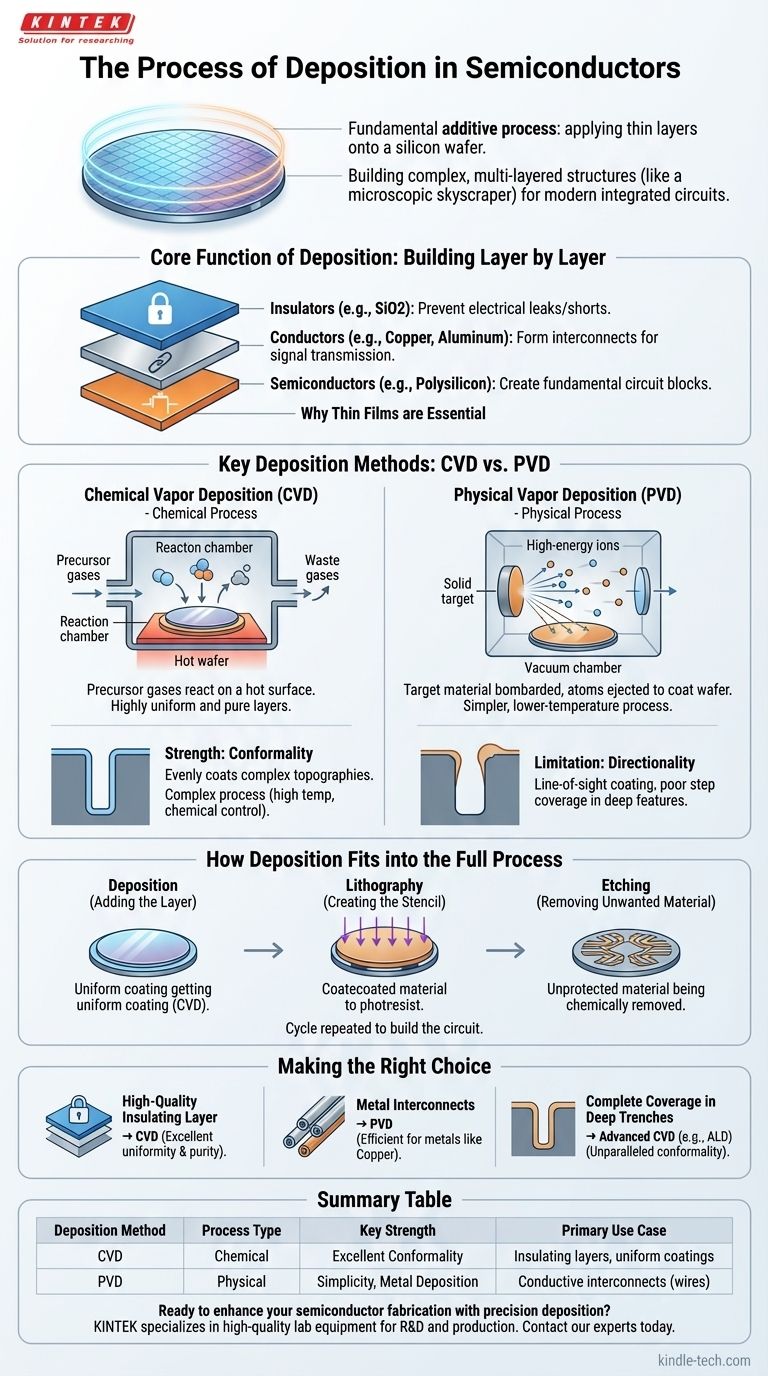

半導体製造において、成膜はシリコンウェハー上に材料の薄層を塗布する基本的なプロセスです。 これは純粋に付加的なプロセスであり、絶縁体、導体、半導体などの材料が、多くの場合、数原子層ずつウェハー表面に成長またはコーティングされます。これは、現代の集積回路を形成する複雑な多層構造を構築するための主要な方法です。

理解すべき重要な概念は、成膜がウェハーに均一な材料層を追加することであるということです。これは、フォトリソグラフィ(層のパターン形成)やエッチング(層の一部を選択的に除去)とは異なり、これらは製造シーケンスにおける別個の後続ステップです。

成膜の核心機能

回路を層ごとに構築する

マイクロプロセッサを、微細な多階建ての超高層ビルと考えてみてください。成膜は、各新しいフロア(絶縁層)や壁内の配線(導電層)を追加するプロセスです。

このプロセスは何百回も繰り返され、現代のチップの複雑な垂直構造が構築されます。各成膜層の品質と精度は、最終的なデバイスの性能にとって極めて重要です。

薄膜が不可欠な理由

成膜によって作られる薄膜は、特定の重要な機能を果たします。

- 絶縁体(例:二酸化ケイ素、窒化ケイ素)は、異なるコンポーネント間での電流の漏れや短絡を防ぎます。

- 導体(例:銅、アルミニウム、タングステン)は、トランジスタ間で信号を伝達する微細な配線、すなわち「相互接続」を形成します。

- 半導体(例:ポリシリコン)は、トランジスタのゲートなど、回路の基本的な構成要素を作成するために使用されます。

主要な成膜方法:CVD vs. PVD

多くの特定の技術がありますが、ほとんどすべての成膜プロセスは、化学気相成長(CVD)と物理気相成長(PVD)という2つの主要なファミリーに分類されます。

化学気相成長(CVD)

CVDは化学プロセスです。前駆体ガスが、加熱されたウェハーを含む反応チャンバーに導入されます。

これらのガスは高温表面で反応し、目的の材料の固体薄膜を残し、他の気体副生成物を放出します。これらはその後排気されます。この方法は、非常に均一で純粋な層を生成することで知られています。

物理気相成長(PVD)

PVDは物理プロセスであり、原子レベルのスプレー塗装に例えられることが多いです。真空チャンバー内で、固体源材料(「ターゲット」と呼ばれる)が高エネルギーイオンで衝撃されます。

この衝撃により、ターゲットから原子が叩き出されます。これらの原子は真空を通過し、ウェハーをコーティングして、原子ごとに薄膜を形成します。

トレードオフの理解

CVDとPVDの選択は、成膜される材料と層の構造要件によって決まります。

CVD:コンフォーマリティ vs. 複雑性

CVDの強みは、そのコンフォーマリティ(段差被覆性)です。化学反応が表面のどこでも起こるため、ウェハーの地形にある非常に深く狭い溝の底面と側面を均一にコーティングできます。

トレードオフは複雑性です。CVDは多くの場合、高温を必要とし、層の純度を確保し欠陥を防ぐために精密に制御されなければならない揮発性の化学反応を伴います。

PVD:単純性 vs. 方向性

PVDは多くの場合、より単純で低温のプロセスであり、CVDの高温に耐えられない金属を成膜するのに理想的です。

その主な限界は方向性です。原子がターゲットからウェハーへ「見通し線」で移動するため、PVDは深い特徴の側壁を均一にコーティングするのに苦労することがあり、これは「ステップカバレッジ」が悪いという問題として知られています。

成膜が全プロセスにどのように適合するか

一部の製造ガイドで説明されている手順は混乱を招く可能性があります。成膜は、何度も繰り返される3段階サイクルの最初の部分にすぎません。

ステップ1:成膜(層の追加)

窒化ケイ素などの材料の均一な層が、CVDなどの方法を使用してウェハーの全面に成膜されます。

ステップ2:リソグラフィ(ステンシルの作成)

フォトレジストと呼ばれる感光性材料が成膜された層の上に塗布されます。その後、パターン化されたマスクを通してUV光に露光され、パターンが現像されて保護ステンシルが作成されます。

ステップ3:エッチング(不要な材料の除去)

化学的またはプラズマエッチングプロセスにより、フォトレジストステンシルで保護されていない領域の窒化ケイ素が除去されます。最後に、残ったフォトレジストが剥離され、目的の回路パターンが残ります。

目標に合った適切な選択をする

成膜方法の選択は、集積回路内の特定の層の機能によって完全に決まります。

- 高品質の絶縁層(例:トランジスタゲート酸化膜)の作成が主な焦点である場合: 化学気相成長(CVD)は、その優れた均一性と純度から推奨される方法です。

- 金属相互接続(配線)の作成が主な焦点である場合: 物理気相成長(PVD)は、銅やアルミニウムなどの金属を成膜する効率性から一般的に使用されます。

- 深く狭い溝での完全な被覆を確保することが主な焦点である場合: 比類のないコンフォーマリティを持つ原子層堆積(ALD)のような高度な技術(CVDの精密なサブタイプ)が必要です。

最終的に、成膜を習得することは、その後の各パターニングおよびエッチングステップの基盤を正確に構築するために、適切な付加技術を選択することにかかっています。

要約表:

| 成膜方法 | プロセスタイプ | 主な強み | 主な用途 |

|---|---|---|---|

| 化学気相成長(CVD) | 化学的 | 優れたコンフォーマリティ | 絶縁層、均一なコーティング |

| 物理気相成長(PVD) | 物理的 | 単純性、金属成膜 | 導電性相互接続(配線) |

精密な成膜で半導体製造プロセスを強化する準備はできていますか? KINTEKは、半導体の研究開発および生産向けに高品質の実験装置と消耗品を専門としています。均一な絶縁層用のCVDシステム、または信頼性の高い金属相互接続用のPVDツールが必要な場合でも、当社のソリューションは現代のチップ製造の厳しい要求を満たすように設計されています。今すぐ専門家にお問い合わせください。お客様のラボの特定の成膜ニーズをサポートし、より優れた集積回路の構築を支援する方法についてご相談ください。

ビジュアルガイド