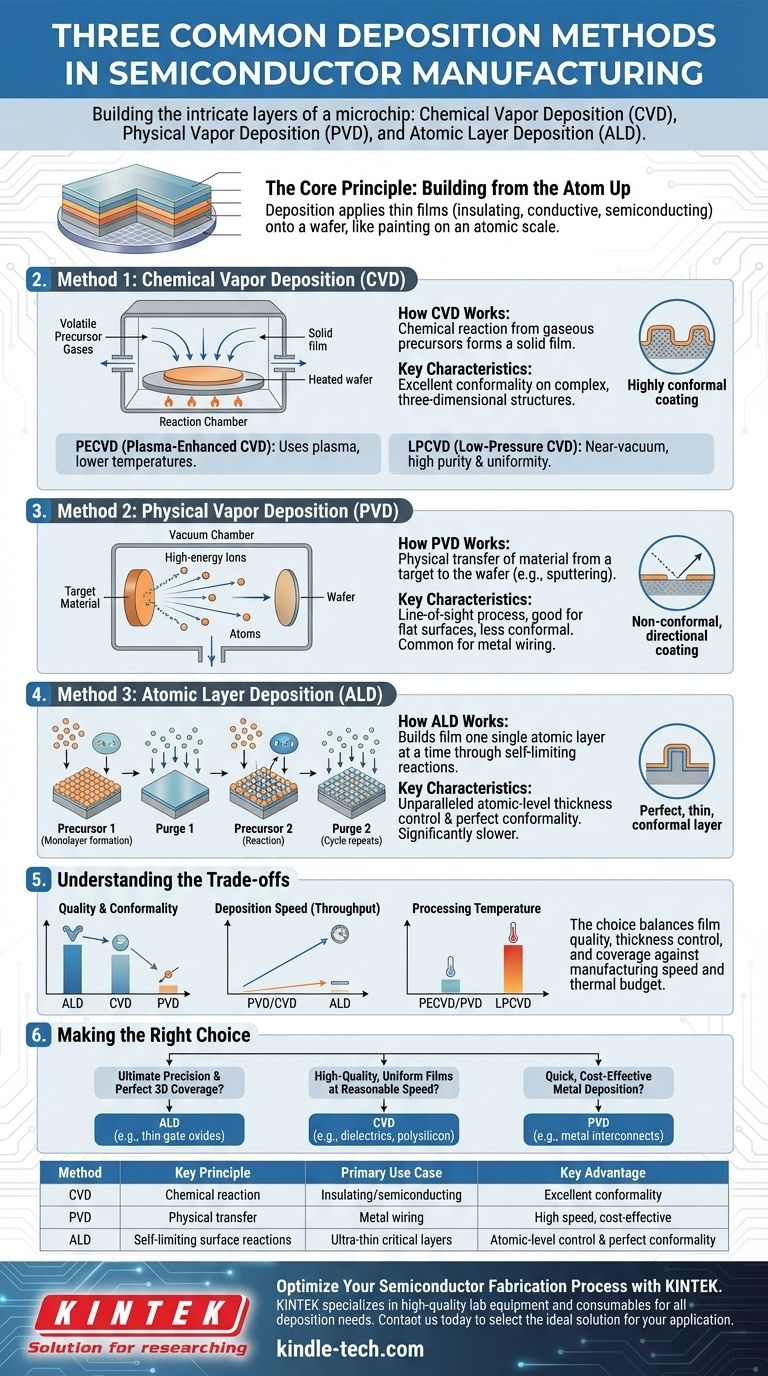

本質的に、半導体製造は、マイクロチップの複雑な層を構築するために、主に3つの成膜方法に依存しています。それは、化学気相成長法(CVD)、物理気相成長法(PVD)、そして原子層堆積法(ALD)です。CVDは気体前駆体からの化学反応を用いて固体膜を形成し、PVDは材料をソースからウェーハへ物理的に移動させ、ALDは究極の精度を実現するために原子層を一つずつ積み重ねて膜を構築します。

これらの方法の選択は決して恣意的ではありません。それは、膜質、膜厚制御、および被覆性の必要性と、製造速度および熱バジェットの実用的な制約とのバランスを取る、根本的なエンジニアリング上の決定です。このバランスを理解することが、現代のチップ製造を理解するための鍵となります。

基本原理:原子から積み上げる

成膜とは、半導体ウェーハ上に様々な材料の薄膜を堆積させるプロセスです。原子スケールでの塗装のようなものだと考えてください。各層はチップの最終的な電子回路において特定の役割を果たします。

これらの層は、絶縁体(二酸化ケイ素など)、導体(銅やアルミニウムなど)、または半導体(ドーピングされたシリコンなど)になり得ます。各層を堆積させるために使用される方法は、その材料の特性とデバイスのアーキテクチャにおける役割に基づいて選択されます。

方法1:化学気相成長法(CVD)

CVDは、高品質で均一な膜を作成するための多用途で広く使用されている技術です。これは、チップ内の多くの絶縁層および半導体層を堆積させるための主力技術です。

CVDの仕組み

CVDプロセスでは、ウェーハを反応チャンバー内に置き、加熱します。その後、最終的な膜に必要な原子を含む揮発性の前駆体ガスが導入されます。これらのガスは、加熱されたウェーハ表面で反応または分解し、固体薄膜を残します。

主な特徴

CVDの主な利点は、高度に均一な(コンフォーマルな)膜を作成できることです。これは、トランジスタが微細化し複雑化するにつれて不可欠となる、複雑な三次元構造を均一にコーティングできることを意味します。

一般的なバリエーション:PECVDとLPCVD

CVDの広いカテゴリーには、いくつかの専門的な技術が含まれます。

- プラズマ強化CVD(PECVD): この方法は、エネルギー豊富なプラズマを使用して化学反応を促進します。これにより、はるかに低温で堆積を行うことができ、ウェーハ上の以前に作製されたコンポーネントへの損傷を防ぐために重要です。

- 低圧CVD(LPCVD): ほぼ真空に近い状態で動作させることにより、LPCVDは望ましくない気相反応を低減します。これにより、ウェーハ全体にわたって非常に高い純度と優れた均一性を持つ膜が得られます。

方法2:物理気相成長法(PVD)

PVD、別名スパッタリングは、CVDとは根本的に異なります。化学反応の代わりに、物理的なプロセスを使用して材料を移動させます。

PVDの仕組み

目的の堆積材料(例:アルミニウムやチタンなどの金属)で作られた固体「ターゲット」を真空チャンバー内に配置します。通常、アルゴンなどの不活性ガスからの高エネルギーイオンがこのターゲットに照射されます。この衝突により、ターゲットから原子が物理的に叩き出され、それらが移動してウェーハをコーティングします。

主な特徴

PVDは一方向性(ライン・オブ・サイト)プロセスです。スパッタされた原子は、スプレー缶からの塗料のように、比較的まっすぐな線で移動します。これにより、平坦な表面への膜堆積には優れていますが、深いトレンチや複雑な地形の側壁をコーティングするのは苦手です。配線用の金属層の堆積に最も一般的に使用されます。

方法3:原子層堆積法(ALD)

ALDは最も先進的な成膜技術であり、膜厚と均一性に関して比類のない制御を提供します。これは、高度に精密なCVDの一種と見なすことができます。

ALDの仕組み

ALDは、自己制限的な一連の反応を通じて、一度に原子層一つずつ膜を構築します。

- 前駆体ガスが導入され、ウェーハ表面と反応して単一の均一な単分子層を形成します。それ以上の反応は起こりません。

- チャンバーがパージされ、過剰な前駆体ガスが除去されます。

- 第2の反応物ガスが導入され、ステップ1の単分子層でのみ反応し、最終膜の1層が完成します。

- チャンバーが再びパージされ、目的の厚さに達するまでサイクルが繰り返されます。

主な特徴

結果として得られるのは、原子レベルの膜厚制御が可能な、完全に均一な膜です。この精度は比類のないものですが、プロセスはCVDやPVDと比較して著しく遅く、最先端のトランジスタにおける最も重要な超薄層にのみ適しています。

トレードオフの理解

成膜方法の選択は、競合する優先順位の重要な評価を伴います。単一の方法がすべての用途に最適ということはありません。

品質と均一性

ALDは可能な限り最高の品質と完全な均一性を提供し、現代のトランジスタの3Dゲートを包み込むために不可欠です。CVDは非常に良好な均一性と品質を提供し、ほとんどの誘電体層および半導体層に適しています。PVDはその一方向性の性質のため、均一性は最も低くなります。

成膜速度(スループット)

PVDとCVDは比較的速いプロセスであり、スループットが重要な製造において必要とされるより厚い膜の堆積に適しています。ALDは、原子層ずつ膜を構築するため、比較すると非常に遅いです。

プロセス温度

成膜に必要な熱は、チップ上の既存の構造に影響を与えたり損傷を与えたりする可能性があります。PECVDとPVDは貴重な低温オプションです。LPCVDなどの他の方法は、目的の膜特性を達成するためにより高い温度を必要とすることが多く、製造フロー内で使用できるタイミングが制限されます。

目標に最適な選択をする

成膜方法の選択は、その技術の強みを、構築される膜層の特定のアーキテクチャ要件と一致させる必要があります。

- 究極の精度と複雑な3D構造に対する完全な被覆が主な焦点である場合: 速度は遅いものの、最も重要な薄いゲート酸化膜やHigh-k誘電体にはALDが不可欠な選択肢となります。

- 合理的な速度で高品質で均一な膜が主な焦点である場合: CVDとそのバリアント(低温の場合はPECVDなど)は、ほとんどの誘電体層およびポリシリコン層の業界の主力です。

- 金属を迅速かつ費用対効果の高い方法で堆積させることが主な焦点である場合: PVD(特にスパッタリング)は、チップを配線する金属相互接続を作成するための頼りになる方法です。

結局のところ、現代の半導体は、それぞれの仕事に最適な特定のツールで堆積された数十の層の複雑なサンドイッチです。

要約表:

| 方法 | 正式名称 | 主要原理 | 主な用途 | 主な利点 |

|---|---|---|---|---|

| CVD | 化学気相成長法 | ガスからの化学反応 | 絶縁層および半導体層 | 複雑な構造に対する優れた均一性 |

| PVD | 物理気相成長法 | 材料の物理的移動(スパッタリング) | 金属配線層 | 高速、金属に対して費用対効果が高い |

| ALD | 原子層堆積法 | 自己制限的な表面反応 | 超薄膜、重要層(例:ゲート酸化膜) | 原子レベルの膜厚制御と完全な均一性 |

KINTEKで半導体製造プロセスを最適化

最適な成膜方法の選択は、半導体デバイスの性能と歩留まりにとって極めて重要です。究極の精度を誇るALD、CVDの多用途な均一性、またはPVDの高速金属堆積のいずれを優先する場合でも、適切な装置を所有することが最も重要です。

KINTEKは、お客様のすべての成膜ニーズに対応する高品質な実験装置と消耗品の提供を専門としています。 私たちの専門知識は、これらの重要なトレードオフを乗り越え、特定のアプリケーションに最適なソリューションを選択するのに役立ち、優れた膜品質と製造効率を保証します。

今すぐお問い合わせください。当社のソリューションがお客様のラボの能力をどのように向上させ、次のイノベーションを推進できるかについてご相談ください。

ビジュアルガイド

関連製品

- 顧客メイド多用途CVDチューブ炉 化学気相成長チャンバーシステム装置

- 精密用途向けCVDダイヤモンドドレッシングツール

- 化学気相成長CVD装置システム チャンバースライド式 PECVD管状炉 液体気化器付き PECVDマシン

- 多ゾーン加熱CVDチューブ炉 マシン 化学気相成長チャンバー システム装置

- 熱管理用途向けCVDダイヤモンド