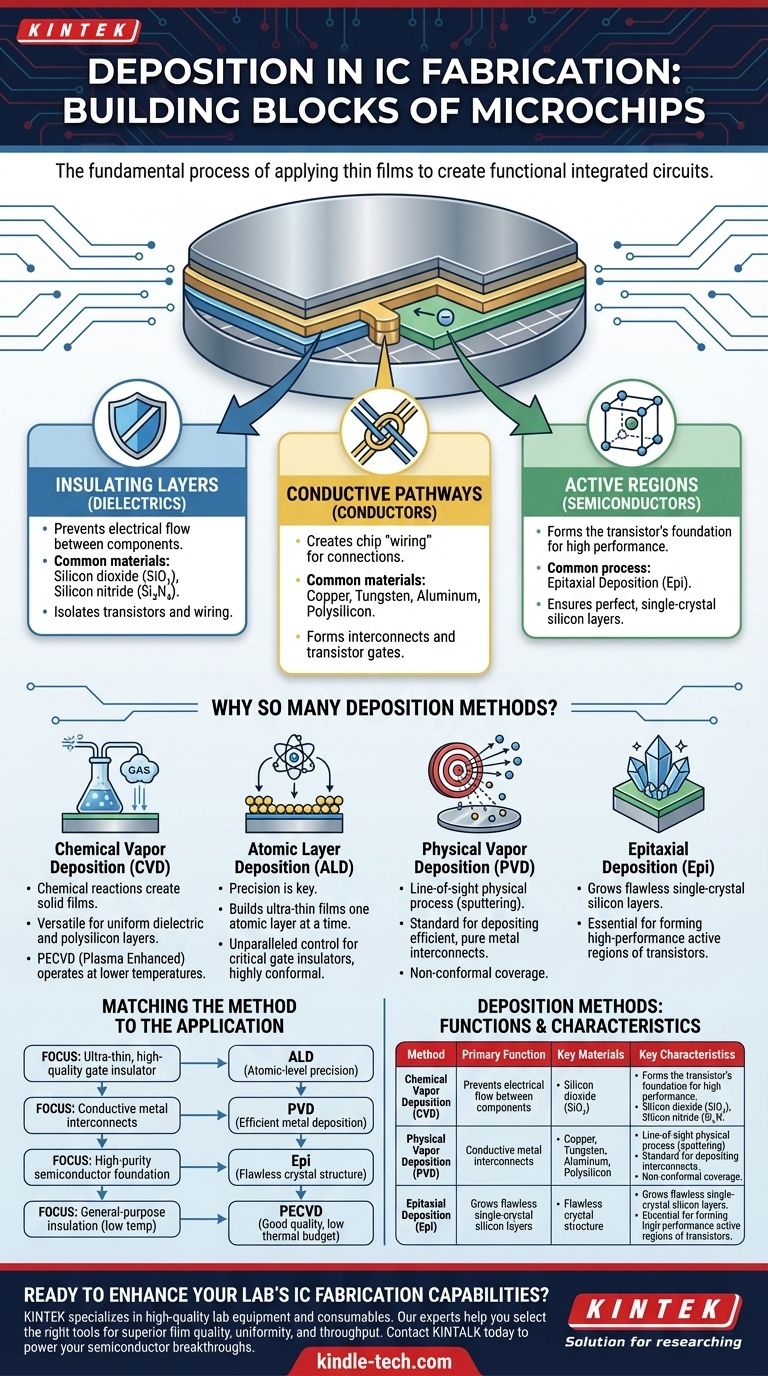

集積回路(IC)の製造において、成膜(Deposition)は、さまざまな材料の薄膜をシリコンウェーハ上に堆積させるために使用される基本的なプロセスです。これらは注意深く制御された層であり、単なるコーティングではなく、トランジスタや配線を形成する導体、絶縁体、半導体として機能するマイクロチップの機能部品を作成するための必須の構成要素となります。

成膜の核心的な目的は、ICの複雑な三次元構造を正確に構築することです。これは製造における「付加」の部分であり、堆積された各層は特定の電気的または構造的な機能を提供し、数十億の微小なコンポーネントが協調して動作することを可能にします。

堆積層の主要な機能

成膜は基本的に、回路内で3つの重要な役割を果たす材料を追加することです。各層は、最終的なデバイスが正しく機能するために必要な特定の目的のために追加されます。

絶縁層(誘電体)の作成

機能的な回路を構築するためには、電気が誤った場所に流れるのを防ぐ必要があります。成膜は、二酸化ケイ素(SiO₂)や窒化ケイ素(Si₃N₄)などの誘電体として知られる絶縁材料を追加するために使用されます。

これらの層は、導電性コンポーネント同士を分離し、短絡を防ぎます。例えば、誘電体膜はトランジスタのゲートをその下のチャネルから分離し、チップの異なる部分を接続する複数の金属配線層を分離します。

導電経路(導体)の形成

トランジスタが構築されたら、それらを接続する必要があります。成膜は、導電性材料を堆積させることにより、チップの「配線」、すなわち相互接続(interconnects)を作成するために使用されます。

銅、タングステン、アルミニウムなどの金属が一般的な選択肢です。このプロセスには、トランジスタのスイッチのオン/オフを制御するゲートを形成するために不可欠な多結晶シリコン(ポリシリコン)の堆積も含まれます。

活性領域(半導体)の構築

トランジスタの性能は、それが構築されるシリコンの品質によって決まります。エピタキシャル成膜(Epi)と呼ばれるプロセスは、出発ウェーハ上に完璧な単結晶シリコン層を成長させるために使用されます。

不純物や欠陥のないこの完璧な層が、トランジスタが動作する活性領域となり、最適な電気特性と高性能を保証します。

なぜこれほど多くの成膜方法があるのか?

CVDからPVD、ALDに至るまで、さまざまな成膜技術が存在するのは、単一の方法がすべての用途に最適ではないためです。技術の選択は、堆積される材料、要求される膜の品質、およびウェーハ上の既存の構造の温度感受性に依存します。

化学気相成長法(CVD)

CVDには、前駆体ガス間の化学反応を利用してウェーハ表面に固体膜を形成する一連の技術(LPCVD、PECVD、APCVD)が含まれます。

この方法は非常に多用途であり、高品質で均一な誘電体層やポリシリコン層を作成するための主力です。特にプラズマ強化CVD(PECVD)は、より低温で動作できるため、以前に構築された層への損傷を防ぐ上で非常に価値があります。

原子層成膜法(ALD)

現代のトランジスタにおける超薄ゲート絶縁膜など、最も重要なコンポーネントにとって、精度がすべてです。原子層成膜法(ALD)は、一度に単一の原子層ずつ膜を構築することにより、これを提供します。

他の方法よりも遅いですが、ALDは厚さと均一性に関して比類のない制御を提供し、デバイスの微細化がナノメートルスケールに縮小するにつれて、これは絶対に不可欠です。

物理気相成長法(PVD)

CVDの化学反応とは異なり、物理気相成長法(PVD)は、スパッタリングとも呼ばれる、線視線(line-of-sight)の物理プロセスです。PVDでは、ターゲット材料がイオンによって衝突され、原子が放出されてウェーハ上に堆積し、コーティングします。

PVDは、相互接続に使用される金属層を堆積させるための標準的な方法です。なぜなら、純粋な金属の膜を敷設するための信頼性が高く効率的な方法だからです。

トレードオフの理解

成膜方法の選択は、常に競合する要件のバランスを取ることを伴います。エンジニアは、構造の幾何学的形状、デバイスの熱的限界、および要求される膜の品質を考慮する必要があります。

コンフォーマルカバレッジと非コンフォーマルカバレッジ

ALDやLPCVDなどの一部のプロセスは、高度にコンフォーマル(均一)な膜を生成します。これは、複雑な3D構造の上面、側面、底面を完全に均一な厚さでコーティングすることを意味します。

対照的に、PVDは線視線プロセスであり、非コンフォーマル(不均一)です。深い狭いトレンチの底面や側面を均一にコーティングするのに苦労することがあり、特定の用途では制限となります。

熱的バジェットの制約

各プロセスステップには熱的バジェット(thermal budget)があります。これは、すでに製造された構造を損傷することなくウェーハがさらされる温度と時間の制限です。

LPCVDなどの高温プロセスは、製造フローの早い段階で使用する必要があります。後続のステップでは、下にあるデリケートなトランジスタ構造を破壊しないように、PECVDやPVDなどの低温法に依存します。

膜の品質とスループットのトレードオフ

堆積膜の完璧さとプロセスの速度の間には、しばしば直接的なトレードオフがあります。

ALDはほぼ完璧な膜を生成しますが、非常に遅いため、最も重要な最も薄い層にのみ適しています。逆に、他の方法は、あまり重要でない層では許容できるものの、膜の品質がわずかに低下する代わりに、より高いスループット(1時間あたりのウェーハ数)を提供する場合があります。

用途に合った方法の選択

作成される層の特定の機能に基づいて、適切な成膜技術が選択されます。

- 超薄で高品質なゲート絶縁膜が主な焦点の場合: 原子レベルの精度が求められるため、原子層成膜法(ALD)が必須の選択肢となります。

- 導電性金属相互接続の堆積が主な焦点の場合: 金属堆積における効率性から、物理気相成長法(PVD)が標準的な主力となります。

- 高品質な半導体基盤が主な焦点の場合: 高性能トランジスタに必要な完璧な結晶構造を作成するために、エピタキシャル成膜(Epi)が使用されます。

- 金属層間の一般的な目的の絶縁が主な焦点の場合: 製造に適した低温で良好な品質が得られるため、プラズマ強化化学気相成長法(PECVD)がよく使用されます。

結局のところ、成膜はIC製造の熟練した技術であり、単純なシリコンウェーハを強力なプロセッサに変える、層ごとの正確な構築を可能にします。

要約表:

| 成膜方法 | 主な機能 | 主要材料 | 主な特徴 |

|---|---|---|---|

| 化学気相成長法 (CVD) | 誘電体およびポリシリコン層 | SiO₂, Si₃N₄, ポリシリコン | 多用途、均一な膜 |

| プラズマ強化CVD (PECVD) | 低温絶縁 | SiO₂, Si₃N₄ | 低い熱的バジェット、良好な均一性 |

| 原子層成膜法 (ALD) | 超薄ゲート絶縁膜 | High-k誘電体 | 原子レベルの精度、高い均一性 |

| 物理気相成長法 (PVD) | 金属相互接続 | 銅、アルミニウム、タングステン | 効率的な金属堆積、線視線 |

| エピタキシャル成膜 (Epi) | 高品質な半導体基盤 | 単結晶シリコン | 高性能トランジスタのための完璧な結晶構造 |

ラボのIC製造能力を向上させる準備はできましたか? 成膜プロセスの精度と品質は、成功に不可欠です。KINTEKは、研究から生産までのすべての成膜ニーズに対応する高品質なラボ機器と消耗品の専門サプライヤーです。当社の専門家が、優れた膜品質、均一性、スループットを達成するための適切なツールの選択をお手伝いします。

今すぐKINTALKにご連絡いただき、当社のソリューションが半導体技術におけるお客様の次のブレークスルーをどのように推進できるかをご相談ください。

ビジュアルガイド