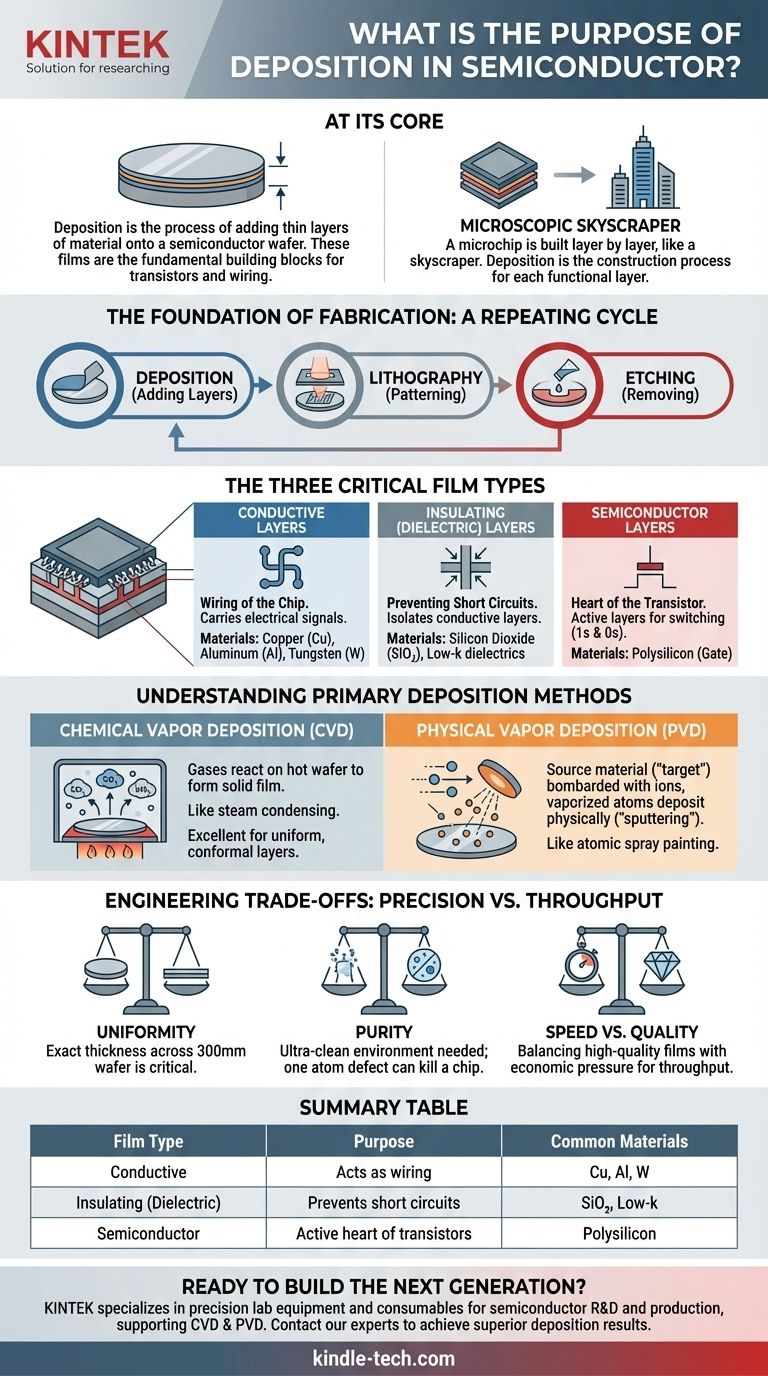

本質的に、成膜とは、半導体ウェハー上に材料の薄い層を追加するプロセスです。これらの膜は、多くの場合、わずか数原子の厚さしかなく、トランジスタ、コンデンサ、およびそれらを接続する配線を形成する複雑な三次元構造を構築するために使用される基本的な構成要素です。成膜がなければ、シリコンウェハーは白紙のままであり、集積回路の作成は不可能でしょう。

マイクロチップは単一のブロックから彫り出されるのではなく、微細な超高層ビルディングのように、層ごとに積み重ねられて構築されます。成膜は、導電性、絶縁性、半導性のいずれであっても、これらの機能層をそれぞれ追加するための基本的な構築プロセスです。

製造の基盤:層ごとに構築する

マイクロチップの製造を、彫刻(材料を削り取る)としてではなく、超精密な3Dプリンティングの一種として考えてみてください。プロセスは、ウェハーとして知られる、手つかずの円形のシリコンディスクを基盤として始まります。

製造プロセス全体は、層の追加(成膜)、パターニング(リソグラフィ)、および選択された部分の除去(エッチング)という繰り返しのサイクルを含みます。成膜は、このサイクルの重要な最初のステップであり、チップのアーキテクチャの各新しいレベルのための原材料を作成します。

半導体における3つの重要な膜タイプ

成膜は、単一の種類の材料を追加することだけではありません。その目的は、それぞれがチップの機能において特定の役割を果たす、異なる電気的特性を持つ様々な膜を堆積させることです。

導電層:チップの配線

これらの膜は、チップ上の異なるコンポーネント間で電気信号を伝達する微細な配線および相互接続として機能します。

銅(Cu)、アルミニウム(Al)、タングステン(W)などの材料が堆積され、電流が流れる経路が作成されます。これらの導電層がなければ、トランジスタは孤立した島となり、通信する手段がありません。

絶縁(誘電体)層:短絡の防止

これらの膜は電気絶縁体であり、電気を伝導しません。その主な役割は、導電層を互いに絶縁することです。

二酸化ケイ素(SiO2)やより高度な低誘電率誘電体などの材料が使用されます。これらは、信号が「短絡」したり、互いに干渉したりするのを防ぎます。これは、何百億ものトランジスタが狭い領域に詰め込まれているため、極めて重要です。

半導体層:トランジスタの心臓部

これらは、トランジスタにオン/オフを切り替える能力を与える「アクティブ」層であり、デジタルロジックの1と0を表します。

ポリシリコンなどの材料を堆積させることは、トランジスタのゲート(電流の流れを制御するコンポーネント)を形成するために不可欠です。これらの堆積された半導体膜の正確な特性が、チップの性能と電力効率を直接決定します。

主要な成膜方法の理解

必要な精度を達成するために、エンジニアはそれぞれ独自の強みを持つ2つの主要な成膜技術ファミリーを使用します。

化学気相成長(CVD)

CVDでは、ウェハーはチャンバーに置かれ、1つまたは複数の反応性ガスにさらされます。これらのガスは高温のウェハー表面で反応し、副産物として目的の材料の固体膜を残します。

これは、冷たい窓に蒸気が凝縮するようなものですが、水ではなく、化学反応によって固体で超高純度の膜が形成されます。CVDは、複雑な3D構造を均一にコーティングする、非常に均一でコンフォーマルな層を作成するのに優れています。

物理気相成長(PVD)

PVDでは、ソース材料(「ターゲット」)が高エネルギーイオンで衝撃され、ターゲットから原子が叩き出されます。これらの気化した原子は真空を通過し、原子のスプレー塗装のような形でウェハー表面に物理的に堆積します。

この方法(しばしばスパッタリングと呼ばれる)は、金属やその他の材料を直接見通し線に沿って堆積させるのに非常に効果的です。

トレードオフ:精度 vs スループット

成膜の目的は完璧な膜を作成することですが、この目標を達成するには、重要な工学的トレードオフを乗り越える必要があります。

均一性の課題

堆積された膜は、300mmウェハー全体でまったく同じ厚さである必要があります。片側からもう片側へのわずか数原子のばらつきでも、何十億ものトランジスタが異なる性能を発揮し、チップの不良につながる可能性があります。

純度の問題

堆積された膜は、非常に純粋でなければなりません。重要な層に単一の不要な異種原子が存在すると、その電気的特性が変化し、チップ全体を機能不全にする欠陥が生じる可能性があります。これには、超クリーンな真空環境が必要です。

速度 vs 品質 のジレンマ

製造はビジネスであり、スループット(1時間あたりのウェハー数)はコストにとって極めて重要です。一般的に、膜をより速く堆積させると、その品質、均一性、または純度が低下する可能性があります。エンジニアは、高品質の膜の必要性と、チップを迅速に生産するという経済的圧力との間で常にバランスを取る必要があります。

これをあなたの目標に適用する方法

成膜の重要性は、半導体業界におけるあなたの特定の焦点によって異なります。

- デバイス性能が主な焦点の場合:堆積された誘電体膜(ゲート絶縁膜など)の品質が、トランジスタの速度と電力漏洩を直接決定します。

- 製造歩留まりが主な焦点の場合:堆積された層の均一性と欠陥のない性質が、1枚のウェハーあたりに多数の動作するチップを生産するための最も重要な要素です。

- 先進アーキテクチャが主な焦点の場合:原子層堆積(ALD)のような新しい成膜技術が、FinFETやGate-All-Around(GAA)のような複雑な3Dトランジスタ構造への移行を可能にします。

最終的に、成膜を理解することは、すべての最新マイクロチップを構築するために使用される基本的な言語を理解することです。

まとめ表:

| 膜の種類 | 目的 | 一般的な材料 |

|---|---|---|

| 導電性 | 電気信号の配線として機能する | 銅 (Cu), アルミニウム (Al), タングステン (W) |

| 絶縁性(誘電体) | 導電層間の短絡を防ぐ | 二酸化ケイ素 (SiO₂), 低誘電率誘電体 |

| 半導体 | トランジスタのアクティブな心臓部を形成する | ポリシリコン |

次世代のマイクロチップを構築する準備はできていますか?堆積された膜の品質は、デバイスの性能と製造歩留まりを直接決定します。KINTEKは、半導体R&Dおよび生産向けの精密ラボ機器と消耗品を専門としています。高度なアーキテクチャを開発している場合でも、高歩留まりのために最適化している場合でも、当社のソリューションはCVDやPVDなどの重要なプロセスをサポートします。今すぐ当社の専門家にご連絡ください。優れた成膜結果を達成する方法についてご相談いただけます。

ビジュアルガイド