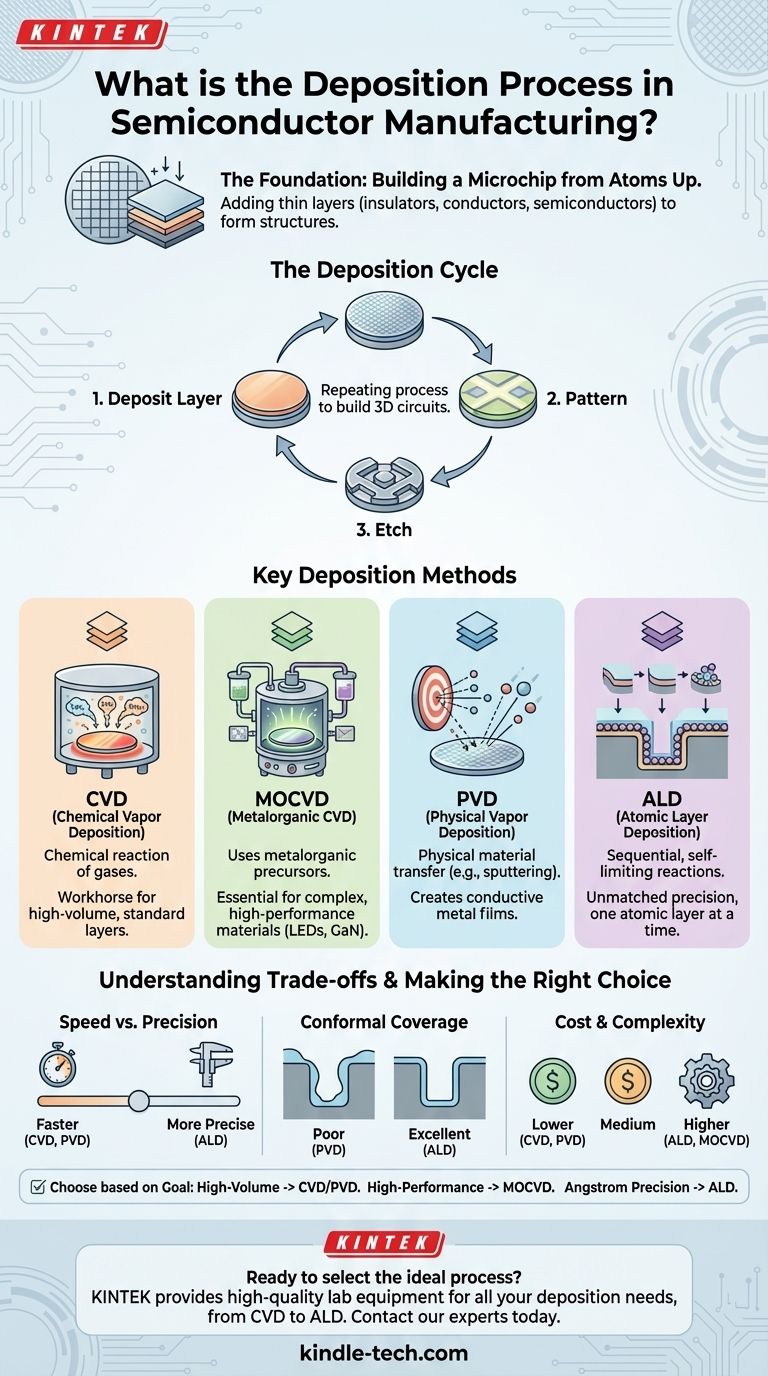

半導体製造において、成膜はシリコンウェハー上に材料の薄い層を形成する基礎的なプロセスです。これらの層は、マイクロチップの複雑な三次元構造を作成するために、パターン形成され、エッチングされる絶縁体、導体、半導体といった基本的な構成要素となります。

成膜は単一の動作ではなく、チップを層ごとに構築するための高度に制御された技術群です。技術の選択は、製造プロセスの各特定のステップにおいて、速度、精度、および材料特性の必要性のバランスを取る、重要なエンジニアリング上の決定となります。

成膜の目的:原子からマイクロチップを構築する

成膜は、半導体製造の繰り返しサイクルにおける核となるステップです。エンジニアは層を繰り返し成膜し、フォトリソグラフィーを使用してパターンを形成し、不要な材料をエッチングして回路を形成します。

絶縁体から導体へ

成膜は、機能するトランジスタに必要なあらゆる種類の材料を形成するために使用されます。これには、配線を互いに絶縁する誘電体膜、配線や相互接続を形成する導電性金属膜、およびトランジスタチャネルを形成する結晶性半導体膜が含まれます。

原子レベルで精密な構造の作成

成膜される層は信じられないほど薄く、多くの場合、オングストロームまたはナノメートル単位(時にはわずか数原子の厚さ)で測定されます。この成膜プロセスの品質は、チップの最終的な性能、消費電力、および信頼性に直接影響します。

主要な成膜方法とその役割

成膜される材料や、膜の厚さ均一性、複雑な非平面表面をどれだけうまく覆うかといった必要な特性に応じて、異なる方法が使用されます。

化学気相成長法(CVD)

CVDは、業界の主力技術です。前駆体ガスをチャンバーに流し込み、そこで高温のウェハー表面で反応させ、固体の薄膜を残します。名称の「気相(Vapor)」は、これらの気体状の化学前駆体を指します。

MOCVDに焦点を当てる

CVDの専門的かつ重要なサブセットが有機金属化学気相成長法(MOCVD)です。有機金属化合物が前駆体として使用され、LEDや高出力トランジスタのようなデバイス向けに高品質で複雑な半導体材料を作成するために不可欠です。

MOCVDは、高精度と材料の柔軟性を大量生産で達成できる能力が高く評価されており、高度なチップ設計にとって費用対効果の高い方法となっています。

物理気相成長法(PVD)

CVDの化学反応とは異なり、PVD法は材料を物理的にウェハー上に転送します。一般的な技術はスパッタリングで、目的の材料で作られたターゲットにイオンを衝突させ、原子を叩き出してウェハー上に付着させます。

原子層堆積法(ALD)

ALDは利用可能な最も精密な方法です。ウェハーを連続的な自己制限的な化学反応に曝すことで材料を構築し、一度に正確に1原子層を堆積させます。この比類のない制御は、現代の最先端トランジスタにおけるゲート酸化膜やその他の極薄膜を作成するために不可欠です。

トレードオフの理解

単一の成膜方法がすべてのアプリケーションに完璧であるわけではありません。選択には常に競合する要因のバランスを取ることが伴います。

速度 vs. 精度

層を成長させる速度と、それをどれだけ正確に制御できるかには直接的なトレードオフがあります。CVDのようなプロセスは、ALDよりも一般的に高速でスループットが高いですが、ALDは層ごとの性質上、本質的に低速です。

コンフォーマルカバレッジ

コンフォーマリティ(均一被覆性)とは、複雑な三次元地形の上に均一に膜を被覆する能力のことです。ALDはほぼ完璧なコンフォーマリティを提供し、現代のFinFETトランジスタにおける深い溝や複雑な形状を覆うために不可欠です。CVDは良好なコンフォーマリティを持ちますが、PVDは直線的なプロセスであり、垂直な側壁を均一に被覆するのに苦労します。

コストと複雑さ

これらのプロセスに必要な装置は、コストと複雑さにおいて劇的に異なります。ALDおよびMOCVDシステムは高度に洗練されており高価ですが、最高の精度または特定の材料特性が必要な場合にのみ正当化されます。PVDおよび標準CVDシステムは、重要度の低い層にはより費用対効果が高い場合があります。

目標に合った適切な選択をする

成膜技術の選択は、構築される層の特定の要件によって決定されます。

- 標準的な絶縁層や金属層の大量生産が主な焦点である場合: 化学気相成長法(CVD)と物理気相成長法(PVD)は、速度、コスト、品質の最適なバランスを提供することがよくあります。

- GaNやGaAsのような高性能化合物半導体の作成が主な焦点である場合: 有機金属CVD(MOCVD)は、その精度と複雑な材料組成を制御する能力により、業界標準となっています。

- オングストロームレベルの精度を持つ最先端のロジックトランジスタの構築が主な焦点である場合: 原子層堆積法(ALD)は、その比類のない膜厚制御と複雑な3D構造を均一に被覆する能力により不可欠です。

最終的に、成膜を習得することは、半導体デバイスの各特定の層を正確に構築するための適切なツールを選択することに尽きます。

要約表:

| 方法 | 正式名称 | 主な特徴 | 主な用途 |

|---|---|---|---|

| CVD | 化学気相成長法 | ウェハー表面でのガスの化学反応 | 標準層の大量生産 |

| MOCVD | 有機金属化学気相成長法 | 複雑な材料に有機金属前駆体を使用 | LED、高出力トランジスタ(GaN、GaAs) |

| PVD | 物理気相成長法 | 材料の物理的転送(例:スパッタリング) | 導電性金属層 |

| ALD | 原子層堆積法 | 一度に1原子層を堆積 | 先進トランジスタ用の極薄で精密な膜 |

半導体製造に最適な成膜プロセスを選択する準備はできていますか? 適切な装置は、プロジェクトが求める正確な材料特性、コンフォーマリティ、およびスループットを達成するために不可欠です。KINTEKは、堅牢なCVDシステムから洗練されたALDソリューションまで、あらゆる成膜ニーズに対応する高品質のラボ機器と消耗品を専門としています。当社の専門家が、次世代マイクロチップの基盤構築をお手伝いします。今すぐ当社のチームにご連絡ください。お客様の特定のアプリケーション要件についてご相談いただけます。

ビジュアルガイド

関連製品

- RF PECVDシステム RFプラズマエッチング装置

- 伸線ダイス用ナノダイヤモンドコーティングHFCVD装置

- 化学気相成長CVD装置システム チャンバースライド式 PECVD管状炉 液体気化器付き PECVDマシン

- 915MHz MPCVDダイヤモンドマシン マイクロ波プラズマ化学気相成長装置 リアクター

- 顧客メイド多用途CVDチューブ炉 化学気相成長チャンバーシステム装置