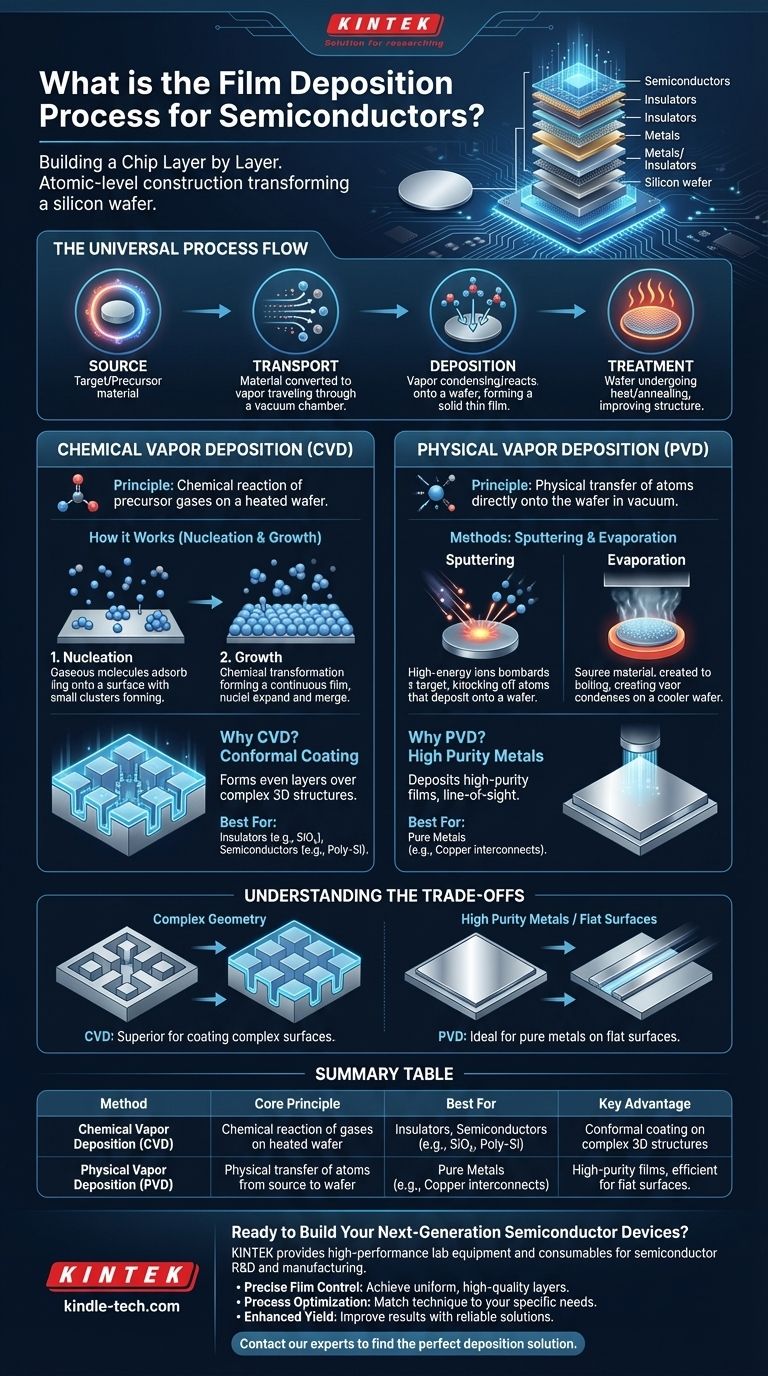

半導体製造において、薄膜形成は、材料の薄く高度に制御された層をシリコンウェーハ上に堆積させる基本的なプロセスです。これは単なるコーティングではなく、マイクロチップの機能層を構築する原子レベルの構築プロセスです。これを実現するための主要な方法は、化学気相成長法(CVD)と物理気相成長法(PVD)の2つです。

薄膜形成の核心的な課題は、原料を蒸気に変換し、それを輸送し、ウェーハ表面で凝縮または反応させて、完全に均一で純粋な固体層を形成させることです。化学的手法(CVD)と物理的手法(PVD)の選択は、堆積させる特定の材料と、それが最終的な集積回路内で果たす役割に完全に依存します。

目標:チップを層ごとに構築する

手法に入る前に、なぜこれらの薄膜が必要なのかを理解することが重要です。現代のマイクロプロセッサは、シリコン基盤の上に何十もの複雑な層が積み重ねられた高層ビルとして構築されています。

「薄膜」とは何か?

薄膜とは、数ナノメートルから数マイクロメートルの厚さを持つ材料の層です。各膜は特定の目的を果たし、導体(銅配線など)、絶縁体(二酸化ケイ素など)、または半導体(トランジスタの活性部分)として機能します。

普遍的なプロセスフロー

特定の技術に関係なく、すべての成膜プロセスは同様のハイレベルなシーケンスに従います。

- ソース(原料): 純粋な原料(ターゲットまたは前駆体と呼ばれる)が選択されます。

- 輸送: この材料は蒸気状態に変換され、通常は真空チャンバー内でウェーハまで輸送されます。

- 堆積(デポジション): 蒸気化された材料が基板(ウェーハ)上に堆積し、固体薄膜を形成します。

- 処理: 膜の結晶構造と特性を改善するために、熱処理(アニーリング)が行われることがあります。

化学気相成長法(CVD):反応による構築

CVDは、その比類のない精度と非常に均一な層を作成できる能力により、半導体業界で最も広く使用されている成膜方法です。

CVDの基本原理

CVDは、最終的な材料を物理的に移動させるのではなく、化学反応を利用します。前駆体ガスが加熱されたウェーハを含むチャンバーに導入されます。これらのガスは高温の表面で反応し、目的の固体材料を堆積させ、揮発性の副産物を残して排気されます。

CVDプロセスの仕組み

このプロセスは、核生成と成長という2つの主要な段階で理解できます。

- 核生成(Nucleation): 気体の前駆体分子がウェーハ表面に吸着されます。

- 成長(Growth): これらの分子は化学的変換を受け、目的の材料の固体の核を形成します。これらの核は拡大・合体し、最終的に連続的で高品質な膜を形成します。

CVDが業界の主力である理由

CVDの主な利点は、コンフォーマル(均一な)コーティングを生成できることです。堆積は化学反応によって駆動されるため、膜はウェーハ上の複雑な三次元構造全体に均等に形成され、これは現代のトランジスタ構造にとって不可欠です。

物理気相成長法(PVD):物質の直接移動

PVDは、ソース材料から原子を物理的にウェーハ表面に直接移動させる一連の技術を包含します。純度を確保するため、これは高真空環境下で行われます。

PVDの基本原理

PVDは基本的に直進性のプロセスです。原子レベルのスプレーペイントのようなもので、個々の原子がソースから放出され、まっすぐ進んで基板をコーティングすると考えてください。

スパッタリング法

スパッタリングは最も一般的なPVD技術です。これには、高エネルギーイオン(通常はアルゴン)でソース材料の固体ターゲットを衝突させます。この衝突により、ターゲットから原子が物理的に叩き出され、それらが移動してウェーハ上に堆積します。

蒸着法

もう一つのPVD技術は蒸着です。このプロセスでは、ソース材料を真空中で加熱して沸騰させ、蒸気を発生させます。この蒸気がより冷たいウェーハに到達し、その表面で凝縮して薄膜を形成します。

トレードオフの理解

CVDとPVDの選択は、どちらが「優れているか」ではなく、構築されている特定の層に適しているのはどちらか、という問題です。

CVDの強み:複雑な幾何学的構造

CVDは、絶縁体(二酸化ケイ素など)や半導体(多結晶シリコンなど)の均一でコンフォーマルな層を作成するのに優れています。その化学的性質により、深いトレンチや複雑なトポグラフィーの内部を均一にコーティングできます。

PVDの強み:高純度金属

PVDは、チップ上の配線(インターコネクト)に使用される高純度金属を堆積させるための主要な方法です。物理プロセスであるため、化学反応によって作成するのが難しい材料を堆積させることができます。主な制限は、複雑な表面での性能が低く、「遮蔽された」領域をコーティングするのに苦労することです。

決定要因:層の機能

決定は、必要な材料とウェーハの表面トポグラフィーに依存します。絶縁体はすべてを完全に覆う必要があるため、CVDが理想的です。金属インターコネクトは高純度を必要とし、しばしば平坦な表面に堆積されるため、PVDの方が効率的な選択肢となります。

目標にプロセスを合わせる

機能的なデバイスを構築するために、エンジニアはこれらの技術を組み合わせて使用し、各特定の層に適切なツールを選択します。

- 複雑な表面上に高品質で均一な絶縁層を作成することに主な焦点を当てる場合: CVDは、その優れたコンフォーマルコーティング能力により、決定的な選択肢となります。

- 電気配線用の純粋な金属膜を堆積させることに主な焦点を当てる場合: PVD、特にスパッタリングは、その速度、純度、制御性により業界標準となっています。

- 完璧な結晶性半導体層を成長させることに主な焦点を当てる場合: 膜の正確な核生成と成長を管理するために、高度に制御されたCVD技術が必要になります。

結局のところ、これらの成膜プロセスは、空白のシリコンウェーハを強力で複雑な集積回路に変えるための不可欠な構築技術なのです。

要約表:

| 方法 | 基本原理 | 最適な用途 | 主な利点 |

|---|---|---|---|

| 化学気相成長法(CVD) | 加熱されたウェーハ表面上でのガスの化学反応。 | 絶縁体、半導体(例:SiO₂、多結晶Si) | 複雑な3D構造へのコンフォーマルコーティング。 |

| 物理気相成長法(PVD) | ソースからウェーハへの原子の物理的移動。 | 高純度金属(例:銅インターコネクト) | 高純度膜、平坦な表面に対して効率的。 |

次世代半導体デバイスの構築準備はできましたか?

適切な成膜プロセスの選択は、ラボの成功にとって極めて重要です。KINTEKは、半導体研究開発および製造向けに高性能なラボ用機器と消耗品の提供を専門としています。

当社が実現を支援すること:

- 精密な膜制御: CVDまたはPVDに最適なツールにアクセスし、均一で高品質な層を構築します。

- プロセス最適化: 成膜技術を特定の材料と構造目標に合わせるための機器とサポートを提供します。

- 歩留まり向上: 信頼性の高い業界標準ソリューションにより、結果を改善します。

半導体製造に関するニーズについてご相談ください。今すぐ専門家にお問い合わせいただき、お客様のラボに最適な成膜ソリューションを見つけてください。

ビジュアルガイド

関連製品

- 化学気相成長CVD装置システム チャンバースライド式 PECVD管状炉 液体気化器付き PECVDマシン

- RF PECVDシステム RFプラズマエッチング装置

- ラボおよびダイヤモンド成長用のマイクロ波プラズマ化学気相成長MPCVDマシンシステムリアクター

- 顧客メイド多用途CVDチューブ炉 化学気相成長チャンバーシステム装置

- 熱管理用途向けCVDダイヤモンド