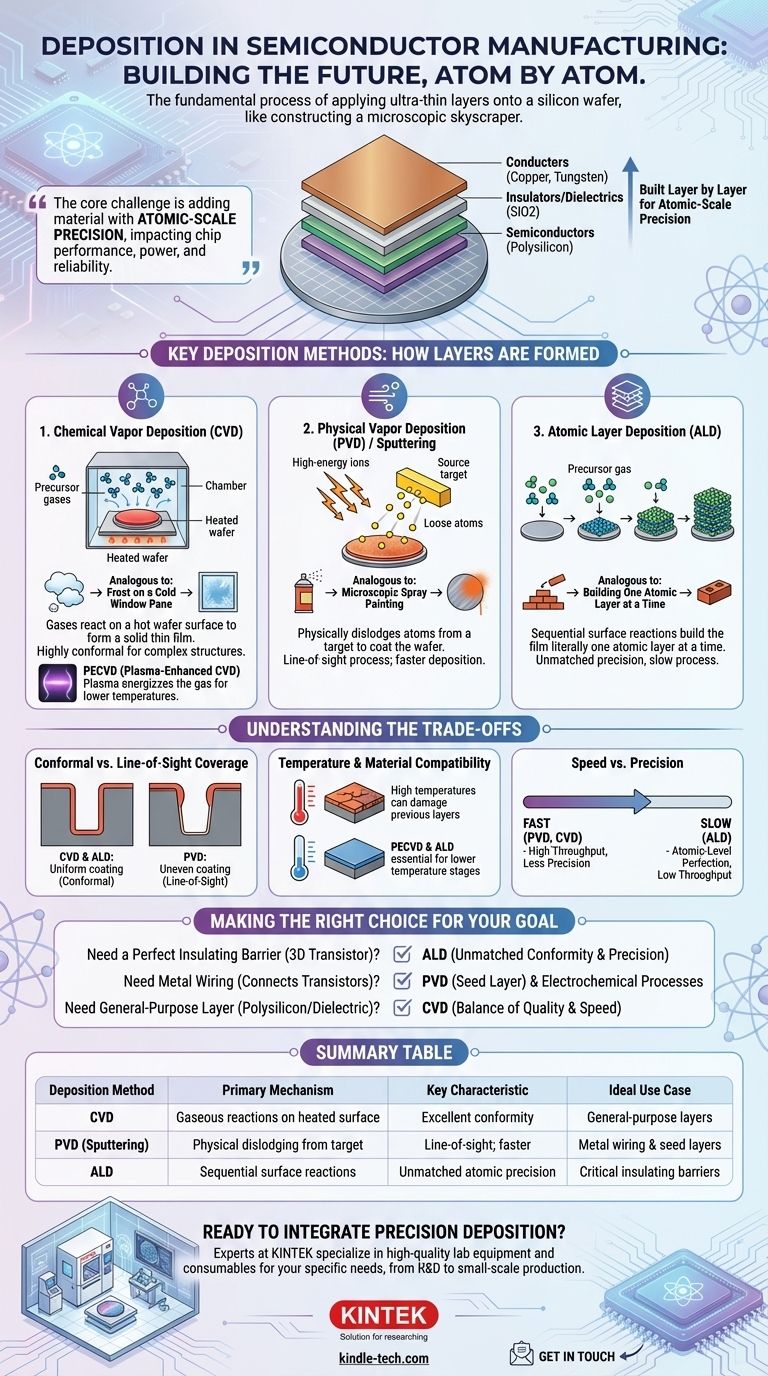

半導体製造において、成膜は基本的なプロセスであり、材料の超薄層をシリコンウェハーに塗布します。これは、微細な超高層ビルを建設するようなもので、各「フロア」は特定の電気的目的に役立つように精密に設計された膜です。これらの層は、しばしば数原子の厚さしかなく、トランジスタ、相互接続、および完全な集積回路を形成するその他のコンポーネントを作成するための不可欠な構成要素です。

成膜の核心的な課題は、単に材料を追加することではなく、原子スケールの精度で行うことです。成膜方法の選択は、チップの性能、消費電力、信頼性に直接影響を与える重要なエンジニアリング上の決定です。

核心機能:チップを層ごとに構築する

現代のマイクロチップは、単一のシリコンブロックから削り出されるわけではありません。代わりに、パターン化された層を繰り返し適用することで上向きに構築され、成膜は各新しい材料層を追加するための主要なプロセスです。

薄膜とは?

「薄膜」とは、数ナノメートルから数マイクロメートルの厚さの材料層です。チップ製造において、これらの膜は一般的に3つのタイプに分類されます:導体(配線用の銅やタングステンなど)、絶縁体または誘電体(短絡を防ぐための二酸化ケイ素など)、および半導体(トランジスタゲート用のポリシリコンなど)です。

目標:絶対的な精度と純度

各回路の機能は、これらの成膜された膜の完璧な厚さ、均一性、および化学的純度に依存します。ウェハー全体でわずかなばらつきや単一の汚染粒子でも、数百万のトランジスタを使い物にならなくし、チップ全体を破壊する可能性があります。

主要な成膜方法:層がどのように形成されるか

数十の成膜技術が存在しますが、それらは主にいくつかの主要なファミリーに分類され、それぞれが異なる物理的メカニズムを持っています。選択される方法は、成膜される材料とその最終デバイスでの役割に完全に依存します。

化学気相成長法 (CVD)

CVDは、前駆体ガスを反応チャンバーに導入し、そこでウェハーが加熱されます。これらのガスはウェハーの高温表面で反応し、固体の薄膜を形成し、ガス状の副産物を残して排出されます。これは、冷たい窓ガラスに水蒸気が凝結して均一な霜の層を形成するのと概念的に似ています。

プラズマ強化CVD (PECVD)のような一般的なバリエーションは、プラズマを使用してガスを活性化し、はるかに低い温度で反応を可能にします。これは、ウェハー上にすでに構築された層への損傷を防ぐために非常に重要です。

物理気相成長法 (PVD)

スパッタリングとしても知られるPVDは、ソース材料(「ターゲット」と呼ばれる)から原子を物理的に叩き出すことで機能します。真空チャンバー内で、ターゲットは高エネルギーイオンで衝突され、原子を剥がします。これらの解放された原子は真空を通過し、ウェハーをコーティングします。

このプロセスは、個々の原子がウェハー表面に「スプレー」される微細なスプレー塗装の一種として最もよく理解できます。

原子層堆積法 (ALD)

ALDは利用可能な最も精密な方法であり、文字通り原子層を1層ずつ構築します。自己制限的な化学反応のシーケンスを使用し、前駆体ガスがチャンバーに次々とパルスされます。各パルスは正確に1つの単分子層の原子を追加します。

他の方法よりもはるかに遅いですが、ALDは厚さに対する比類のない制御を提供し、最も複雑な3次元微細構造にも膜が完全に適合することを保証します。

トレードオフの理解

非常に多くの成膜方法が存在することは、中心的なエンジニアリングの真実を浮き彫りにします。つまり、「最良の」単一の技術は存在しないということです。それぞれが速度、材料品質、および複雑なトポロジーをカバーする能力の間で重要なトレードオフを伴います。

コンフォーマル対見通し線カバレッジ

最も重要な区別の一つは、方法が3D構造をどのように扱うかです。CVDとALDは非常にコンフォーマルであり、深いトレンチの内側のような複雑で平坦でない表面に完全に均一な層を堆積させることができます。

対照的に、PVDは見通し線プロセスです。スプレー缶のように、「見える」表面のみをコーティングでき、トレンチの上部では材料が厚く、底部でははるかに薄くなることがよくあります。

温度と材料の適合性

高温は破壊的である可能性があります。一部のCVDプロセスに必要な熱は、以前に堆積された層を損傷したり、材料が互いに拡散して電気的特性を損なったりする可能性があります。これが、PECVDやALDのような低温方法がチップ製造の後期段階で不可欠である理由です。

速度対精度

製造速度(スループット)と膜品質の間には避けられないトレードオフがあります。ALDのようなプロセスは原子レベルの完璧さをもたらしますが、非常に遅いです。そのような精度が必要ない、より厚く、それほど重要でない層の場合、より高速なCVDまたはPVDプロセスの方がはるかに経済的です。

目標に合った適切な選択をする

成膜技術の選択は、常に構築される層の特定の要件によって決定されます。

- 3Dトランジスタで完璧なピンホールフリーの絶縁バリアを作成することが主な焦点である場合:原子スケールでの比類のないコンフォーマル性と精度のため、ALDが唯一の選択肢です。

- トランジスタを接続する金属配線を堆積させることが主な焦点である場合:PVD(初期の「シード」層を作成するため)と他の電気化学プロセスの組み合わせが業界標準です。

- 汎用ポリシリコンまたは誘電体層を堆積させることが主な焦点である場合:CVDの一種が、膜品質、コンフォーマル性、および製造速度の理想的なバランスを提供することがよくあります。

最終的に、成膜を習得することは、現代の集積回路の各特定のナノメートルスケールの層を構築するための理想的なツールを選択することです。

要約表:

| 成膜方法 | 主要メカニズム | 主な特徴 | 理想的な使用例 |

|---|---|---|---|

| 化学気相成長法 (CVD) | 加熱されたウェハー表面でのガス状化学反応。 | 複雑な3D構造に対する優れたコンフォーマル性。 | 汎用誘電体および半導体層。 |

| 物理気相成長法 (PVD / スパッタリング) | ターゲット材料からの原子の物理的な叩き出し。 | 見通し線カバレッジ;より速い成膜。 | 金属配線およびシード層。 |

| 原子層堆積法 (ALD) | 自己制限的、連続的な表面化学反応。 | 比類のない原子スケールの精度とコンフォーマル性。 | 高度な3Dトランジスタにおける重要な絶縁バリア。 |

研究室のワークフローに精密成膜を統合する準備はできていますか?

適切な成膜技術の選択は、半導体研究やデバイス製造の性能にとって非常に重要です。KINTEKの専門家は、お客様の特定の成膜ニーズに合わせた高品質の実験装置と消耗品の提供を専門としています。

原子スケールの精度を達成することの課題を理解しており、R&D、プロセス開発、小規模生産のいずれに焦点を当てているかに関わらず、理想的なソリューションを選択するお手伝いをいたします。

お客様の研究室の能力を高め、プロジェクトを推進する方法について話し合うために、今すぐお問い合わせください。

ビジュアルガイド