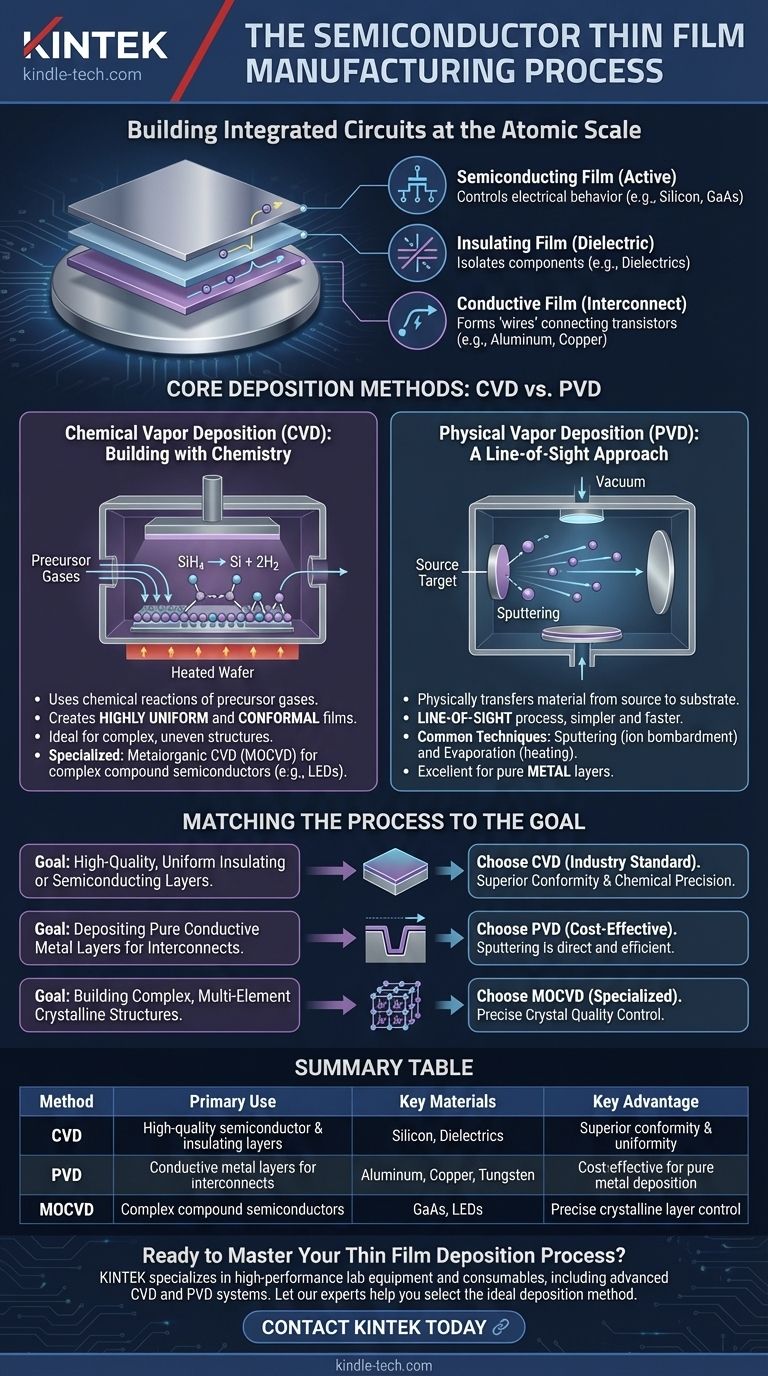

その核心において、半導体薄膜製造とは、基板(通常はシリコンウェーハ)上に、非常に薄く、精密に制御された様々な材料の層を堆積させるプロセスです。これは主に2つの方法で行われます。化学気相成長法(CVD)は、化学反応を利用して層を構築し、物理気相成長法(PVD)は、材料を物理的にウェーハ上に転送します。これらの方法の選択は、堆積される特定の材料と、最終的なマイクロチップ内でのその意図された電気的機能によって決定されます。

薄膜堆積の目的は、単に表面をコーティングすることではありません。それは、集積回路の基本的な構成要素であるトランジスタ、絶縁体、および配線を、一度に1層ずつ構築するために使用される原子スケールの構築プロセスです。

基盤:なぜ薄膜が不可欠なのか

製造プロセスを理解するためには、まずフィルム自体の目的を理解する必要があります。現代のマイクロチップは、これらの層の何百もの層から構築された三次元構造です。

基板から回路へ

プロセスは、多くの場合、結晶シリコンのウェーハである、手付かずの平坦な基板から始まります。

各薄膜層は、特定の電気的特性を持つ新しい材料を追加し、集積回路の複雑なアーキテクチャを徐々に構築していきます。

各層の役割

これらの層は交換可能ではありません。それらは、トランジスタのような能動部品を形成するために連携して機能する3つの主要なカテゴリに分類されます。

- 半導体膜:これらは、電気的挙動が制御される能動層であり、多くの場合、シリコン(Si)またはガリウムヒ素(GaAs)のようなより複雑な化合物半導体でできています。

- 絶縁膜(誘電体):これらの膜は、電気が流れてはならない場所への流れを防ぎます。それらは異なる導電部分を互いに絶縁します。

- 導電膜:これらは、チップ上の数百万または数十億のトランジスタを接続する「配線」または相互接続を形成します。材料には、アルミニウム、銅、タングステンなどの金属が含まれます。

主要な堆積方法:CVD vs. PVD

薄膜製造の大部分は、2つの技術ファミリーに分類されます。選択される方法は、構築される層の品質と機能にとって重要です。

化学気相成長法(CVD):化学で構築する

CVDは、その精度により、最高品質の半導体および誘電体膜を作成するための主要なプロセスです。

このプロセスには、ウェーハを含む反応炉チャンバーに前駆体ガスを導入することが含まれます。これらのガスは、高温のウェーハ表面で反応し、目的の材料の固体膜を残します。例えば、シランガス(SiH4)は、純粋なシリコン(Si)の固体膜を堆積させるために使用されます。

この方法は、非常に均一でコンフォーマルな膜を作成するのに優れており、これは、層の厚さが、部分的に構築されたチップの複雑で不均一な地形上でも一貫していることを意味します。

より深く掘り下げる:有機金属CVD(MOCVD)

複数の元素(GaAsなど)からなる複雑な半導体の場合、MOCVDと呼ばれる特殊な変種が使用されます。

この高度なプロセスは、有機金属化合物前駆体を使用して完全な結晶層を成長させ、LEDや高度なトランジスタのような高性能デバイスの作成を可能にします。

物理気相成長法(PVD):見通し線アプローチ

PVDは、材料を供給源(または「ターゲット」)から基板に物理的に移動させることで機能します。これは、スプレー塗装に似ていますが、原子レベルで行われます。

これは「見通し線」プロセスであり、堆積された原子が供給源からウェーハまで直線的に移動することを意味します。CVDよりも単純で、多くの場合高速です。

一般的なPVD技術

最も一般的なPVD方法は、スパッタリング(ターゲット材料がイオンで衝撃され、原子が放出される)と蒸着(ターゲットが気化するまで加熱される)の2つです。これらの方法は、非常に純粋な金属層を堆積させるのに優れています。

トレードオフを理解する

どちらの方法も普遍的に優れているわけではありません。それらは特定の仕事のために選択されるツールです。選択は、性能、材料特性、および複雑さの間の古典的なエンジニアリングのトレードオフです。

CVDを使用する場合

CVDは、コンフォーマリティと膜品質が譲れない場合のデフォルトの選択肢です。

これは、コンポーネントを絶縁する重要な絶縁層と、トランジスタ自体を形成する高純度半導体層を堆積させるために不可欠です。複雑な構造を均一にコーティングする能力が、その決定的な利点です。

PVDを使用する場合

PVDは主に、導電性金属層の堆積に使用されます。

その役割は、配線を形成するためにより広い溝を埋めることであるため、「見通し線」の制限はそれほど懸念されません。これは、アルミニウム、銅、または窒化チタン(TiN)のようなバリア金属の層など、チップの相互接続配線を作成するための信頼性が高く費用対効果の高い方法です。

最終ステップ:膜のパターニング

堆積だけでは回路は作成されません。膜がウェーハ全体に均一に堆積された後、フォトリソグラフィとエッチングを使用して材料が除去され、最終的な回路コンポーネントを定義する正確なパターンが残されます。

プロセスを目標に合わせる

正しい選択をするには、堆積技術を作成している層の機能に合わせる必要があります。

- 高品質で均一な絶縁層または半導体層の作成が主な焦点である場合:CVDは、その優れたコンフォーマリティと化学的精度により、業界標準です。

- 相互接続用の純粋な導電性金属層の堆積が主な焦点である場合:スパッタリングのようなPVD技術は、最も直接的で費用対効果の高いソリューションです。

- 高度なデバイス用の複雑な多元素結晶構造の構築が主な焦点である場合:材料の結晶品質を精密に制御するために、MOCVDのような特殊なプロセスが必要です。

最終的に、これらの原子スケールの堆積方法を習得することが、すべての現代エレクトロニクスの絶え間ない小型化と増大するパワーを可能にしています。

要約表:

| 方法 | 主な用途 | 主要材料 | 主な利点 |

|---|---|---|---|

| 化学気相成長法(CVD) | 高品質半導体および絶縁層 | シリコン、誘電体 | 優れたコンフォーマリティと均一性 |

| 物理気相成長法(PVD) | 相互接続用導電性金属層 | アルミニウム、銅、タングステン | 純金属堆積に費用対効果が高い |

| 有機金属CVD(MOCVD) | 複雑な化合物半導体 | GaAs、LED | 精密な結晶層制御 |

薄膜堆積プロセスを習得する準備はできていますか?

次世代トランジスタの開発であろうと、チップの相互接続の最適化であろうと、適切な堆積装置は極めて重要です。KINTEKは、高度なCVDおよびPVDシステムを含む、半導体製造用の高性能ラボ機器と消耗品の提供を専門としています。

当社のソリューションは、最先端のマイクロチップに必要な精密で均一な層を実現するのに役立ちます。当社の専門家が、お客様の特定の材料とアプリケーション目標に最適な堆積方法を選択するお手伝いをいたします。

当社の専門ラボ機器がお客様の半導体研究および生産能力をどのように向上させることができるかについて議論するために、今すぐKINTEKにお問い合わせください。

ビジュアルガイド

関連製品

- 薄膜成膜用アルミニウムコーティングセラミック蒸着用ボート

- 薄膜成膜用タングステン蒸着用ボート

- 電子ビーム蒸着コーティング 無酸素銅るつぼおよび蒸着用ボート

- 高温用途向けモリブデン・タングステン・タンタル蒸着用ボート

- 伸線ダイス用ナノダイヤモンドコーティングHFCVD装置