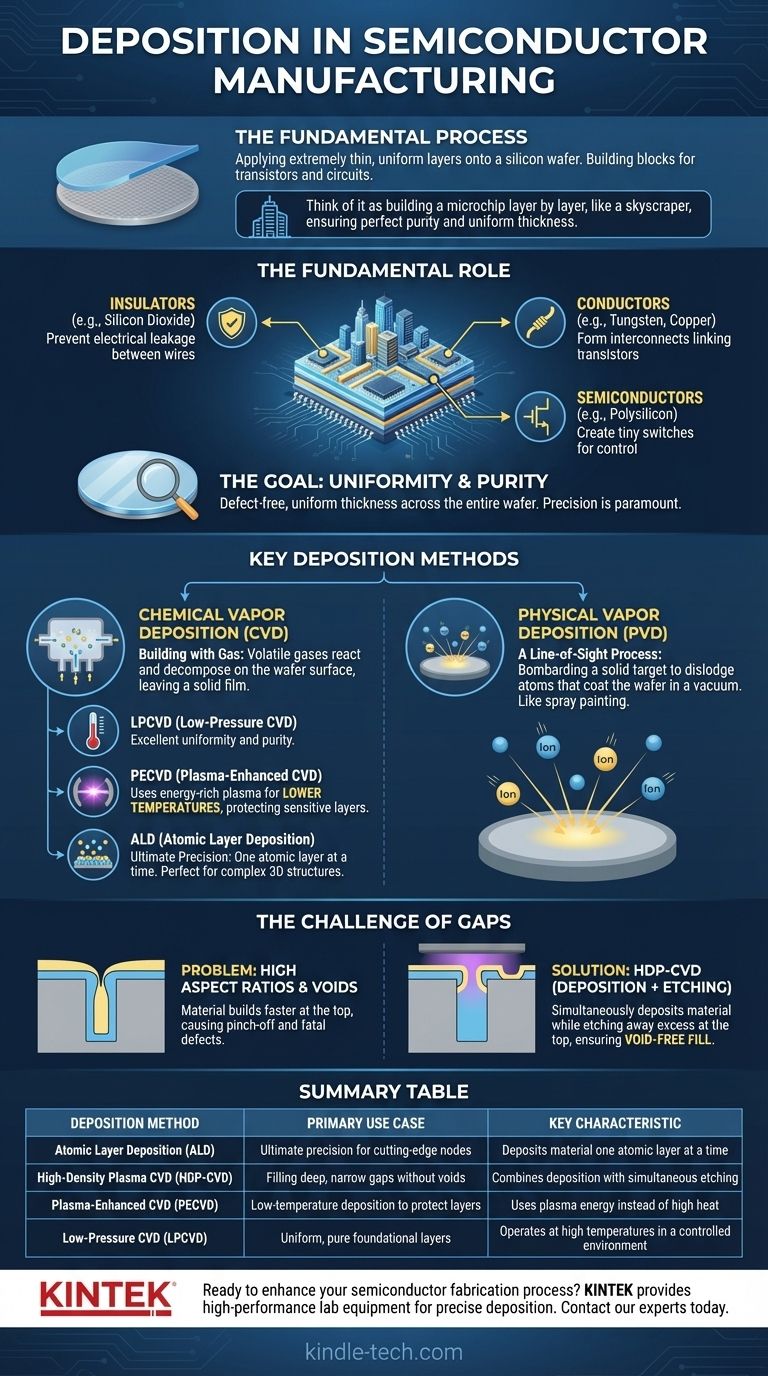

半導体製造において、成膜は、極めて薄く均一な材料層をシリコンウェーハ上に適用する基本的なプロセスです。これらの層は、絶縁体、導体、または半導体であり、トランジスタ、配線、および集積回路の他のコンポーネントを形成する不可欠な構成要素です。これらの膜を成膜するために、さまざまな高度に専門化された技術が使用され、その方法は特定の材料とそのチップ内での構造的役割によって選択されます。

その核心において、成膜は、超高層ビルを階ごとに建設するのと同じように、マイクロチップを層ごとに構築することです。課題は、単に層を追加するだけでなく、それが完全に純粋で、均一な厚さであり、現代のプロセッサの信じられないほど複雑で微細な地形を完璧に埋めることを確実にすることです。

成膜の基本的な役割

成膜は単一の動作ではなく、回路のまさに実体が作成される製造の重要な段階です。それがなければ、シリコンウェーハは空白のままです。

マイクロチップの層を構築する

完成したマイクロプロセッサを、数十億の構造を持つ密集した三次元都市と考えてください。成膜は、その都市のすべてのコンポーネント、つまり基礎、壁、電気配線、それらの間の絶縁を構築するプロセスです。各層はわずか数ナノメートル厚で、ほぼ完璧でなければなりません。

絶縁体、導体、半導体

成膜技術は、回路に必要な3つの主要な種類の材料すべてを適用するために使用されます。

- 二酸化シリコンのような絶縁体は、配線間の電流漏れを防ぐために成膜されます。

- タングステンや銅のような導体は、トランジスタを相互に接続する「配線」や相互接続を形成するために成膜されます。

- ポリシリコンのような半導体は、トランジスタゲート自体、つまり電流の流れを制御する小さなスイッチを作成するために成膜されます。

目標:均一性と純度

あらゆる成膜プロセスの主な目標は、ウェーハの表面全体にわたって欠陥のない膜を均一な厚さで作成することです。微細なばらつき、不純物、または空隙でさえ、チップの故障を引き起こす可能性があり、これらのプロセスの精度が製造歩留まりにとって最も重要になります。

主な成膜方法とその目的

「成膜」という用語は、それぞれ異なる材料、温度、構造要件に合わせて最適化された幅広い技術群を包含します。これらは大きく2つのファミリーに分類されます:化学気相成長(CVD)と物理気相成長(PVD)。

化学気相成長(CVD):ガスで構築する

CVDは最も一般的な技術ファミリーです。このプロセスでは、ウェーハは反応チャンバーに置かれ、1つまたは複数の揮発性ガスに曝されます。これらのガスはウェーハ表面で反応・分解し、固体で高純度の膜を残します。

一般的なCVDのバリエーション

異なる種類のCVDは、主に温度と膜の品質に関連するさまざまな問題を解決するために使用されます。

- LPCVD(低圧CVD):この方法は、高温と低圧を使用します。高熱が化学反応のエネルギーを提供し、優れた均一性と純度を持つ膜が得られます。

- PECVD(プラズマ強化CVD):この方法は、エネルギー豊富なプラズマを使用して化学反応を補助します。この追加されたエネルギーにより、プロセスをはるかに低い温度で実行できます。これは、高温に耐えられない材料(アルミニウムなど)の上に層を成膜する場合に重要です。

原子層堆積(ALD):究極の精度

最も高度で最小のチップ機能には、原子層堆積(ALD)が使用されます。この技術は、ガスを連続的で自己制限的なサイクルで導入することにより、文字通り単一原子層ずつ材料を堆積させます。これにより、膜厚の比類のない制御と、最も複雑な3D構造を完璧にコーティングする能力が提供されます。

物理気相成長(PVD):見通し線プロセス

CVDとは対照的に、PVDは物理プロセスです。これは、目的の材料の固体「ターゲット」に高エネルギーイオンを衝突させ、ターゲットから原子を物理的に叩き出すことを伴います。これらの原子は真空を通過し、ウェーハをコーティングします。これは、スプレー塗装に似た「見通し線」プロセスとしてよく説明されます。

トレードオフの理解:ギャップの課題

トランジスタが縮小するにつれて、材料で満たされなければならないトレンチやギャップは非常に深く狭くなります。これは、成膜技術の進化を推進してきた重大な課題を生み出しています。

高い「アスペクト比」の問題

アスペクト比とは、フィーチャの高さと幅の比率を指します。現代のチップでは、これらの比率は非常に高いです。深く狭いトレンチを従来の成膜プロセスで埋めようとすると、重大な問題が発生します。

ボイドと「ピンチオフ」

標準的な成膜プロセスは、トレンチの底部よりも上部の角に材料が早く堆積する傾向があります。これにより、トレンチが完全に埋まる前に開口部が「ピンチオフ」し、構造内に空洞、つまりボイドが閉じ込められる可能性があります。このボイドは、チップ全体を台無しにする致命的な欠陥です。

HDP-CVDソリューション:成膜とエッチングの組み合わせ

これを解決するために、高密度プラズマCVD(HDP-CVD)と呼ばれるより高度なプロセスが開発されました。この技術は、同じチャンバー内で2つのプロセスを巧みに組み合わせています。

- 成膜:材料がトレンチに堆積されます。

- エッチング:同時に、イオン(アルゴンなど)を使用して、トレンチの上部開口部に堆積した材料を物理的にスパッタリング除去、つまりエッチングします。

この同時エッチング作用により、トレンチは成膜材料が下から上へフィーチャを完全に埋めるのに十分な時間開いたままになり、最高のアスペクト比構造でもボイドのない充填が保証されます。

目標に合った適切な選択をする

成膜方法の選択は、構築される層の特定の要件(材料、構造、およびその下にある層の温度耐性)のバランスを取る問題です。

- 最先端ノード向けの究極の精度と適合性が主な焦点である場合:原子層堆積(ALD)は、1原子ずつ制御できるため標準です。

- ボイドなしで深く狭いギャップを埋めることが主な焦点である場合:高密度プラズマCVD(HDP-CVD)は、成膜とエッチングを組み合わせて完全な充填を保証するため、ソリューションとなります。

- 既存の層を保護するために低温で膜を堆積させることが主な焦点である場合:プラズマ強化CVD(PECVD)は、プラズマが高熱の代わりに反応エネルギーを提供するため、理想的な選択肢です。

- 高温が制約とならない均一で純粋な基礎層が主な焦点である場合:低圧CVD(LPCVD)は、高度に制御された環境で優れた結果を提供します。

各成膜技術の目的を理解することは、現代の半導体製造の複雑さを習得するための第一歩です。

要約表:

| 成膜方法 | 主な用途 | 主な特徴 |

|---|---|---|

| 原子層堆積(ALD) | 最先端ノード向けの究極の精度 | 材料を1原子層ずつ堆積させる |

| 高密度プラズマCVD(HDP-CVD) | ボイドなしで深く狭いギャップを埋める | 成膜と同時エッチングを組み合わせる |

| プラズマ強化CVD(PECVD) | 層を保護するための低温成膜 | 高熱の代わりにプラズマエネルギーを使用する |

| 低圧CVD(LPCVD) | 均一で純粋な基礎層 | 制御された環境で高温で動作する |

半導体製造プロセスを強化する準備はできていますか?

KINTEKは、精密な成膜やその他の重要な半導体製造工程向けに、高性能なラボ機器と消耗品を提供することに特化しています。当社のソリューションは、高歩留まりのチップ生産に不可欠な、均一で欠陥のない層を実現するのに役立ちます。

今すぐ当社の専門家にお問い合わせください。お客様のラボの特定の成膜ニーズをサポートし、イノベーションを推進する方法についてご相談ください。

ビジュアルガイド

関連製品

- 化学気相成長CVD装置システム チャンバースライド式 PECVD管状炉 液体気化器付き PECVDマシン

- 精密用途向けCVDダイヤモンドドレッシングツール

- 高温用途向けモリブデン・タングステン・タンタル蒸着用ボート

- 有機物用蒸発皿

- 電子ビーム蒸着コーティング 無酸素銅るつぼおよび蒸着用ボート