エレクトロニクスの世界では、半導体はその極端な薄さによって定義されます。 半導体が構築されるシリコンウェハーは構造的な完全性のために目に見える厚さを持っていますが、半導体の能動的で機能的な層はナノメートル単位で測定されます。これは人間の髪の毛よりも数千倍も薄いスケールです。最終的に目にする製品であるチップは、特定の目的のために設計された小さくて薄いパッケージです。

半導体の計り知れない力は、その塊からではなく、その機能層の微細な薄さから来ています。この薄さは、現代のコンピューティングを定義する速度、効率、密度を可能にするための意図的なエンジニアリングの選択です。

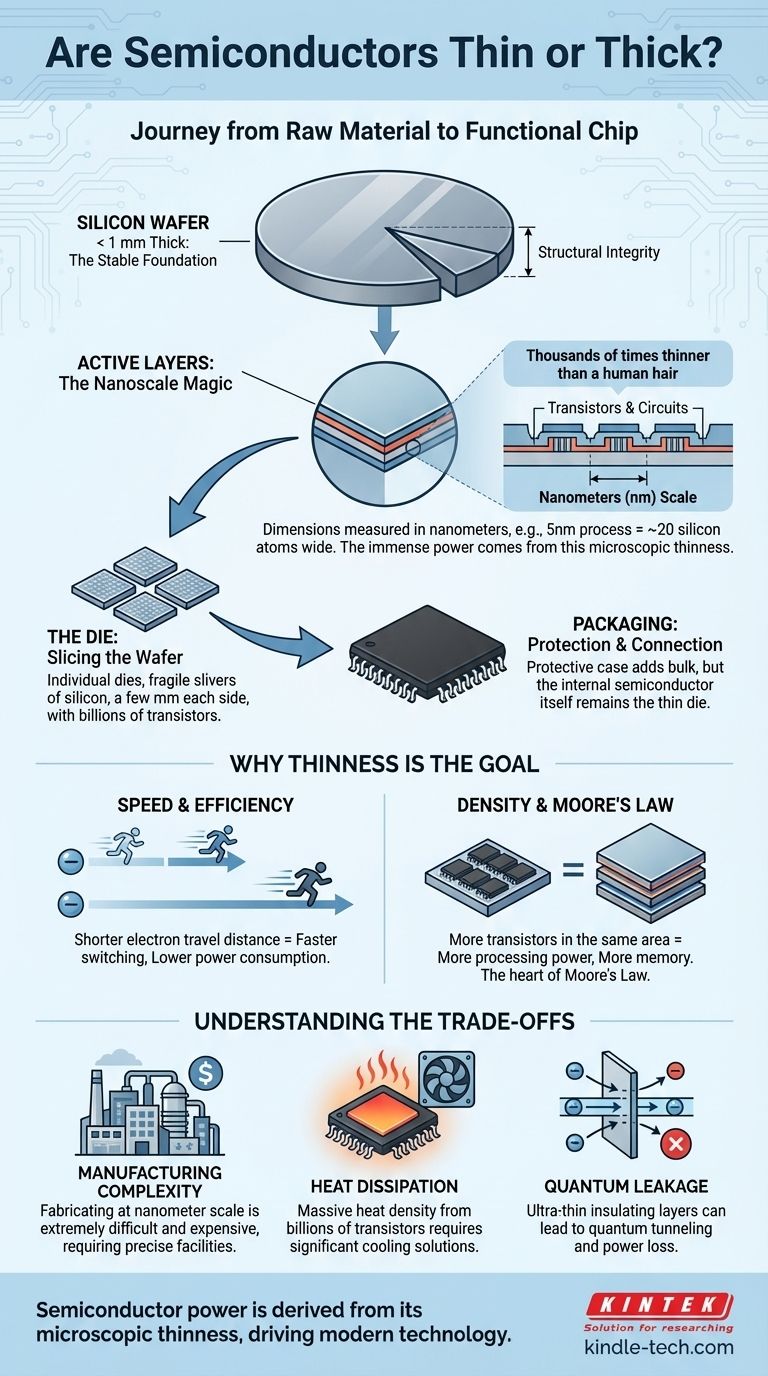

原材料から機能チップへ

半導体の寸法を理解するには、原材料であるシリコンウェハーからパッケージ化されたチップに至るまでの過程を見る必要があります。このプロセスには、比較的「厚い」コンポーネントと信じられないほど「薄い」コンポーネントの両方が含まれます。

シリコンウェハー:安定した基盤

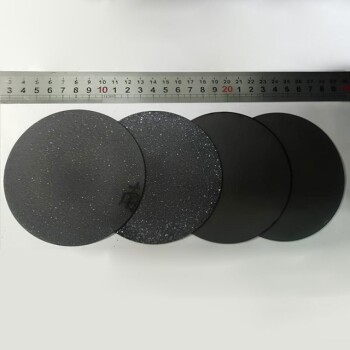

半導体デバイスは、シリコンウェハーの一部としてその生命を始めます。これは、回路を構築するための基板、つまり基盤として機能する、非常に純粋で完全に平坦で剛性のあるディスクです。

典型的なウェハーは直径300mm(約12インチ)で、厚さは1mm未満です。この厚さは、複雑な製造プロセス中にウェハーが破損することなく処理するために必要な機械的安定性を提供する上で重要です。

アクティブ層:魔法が起こる場所

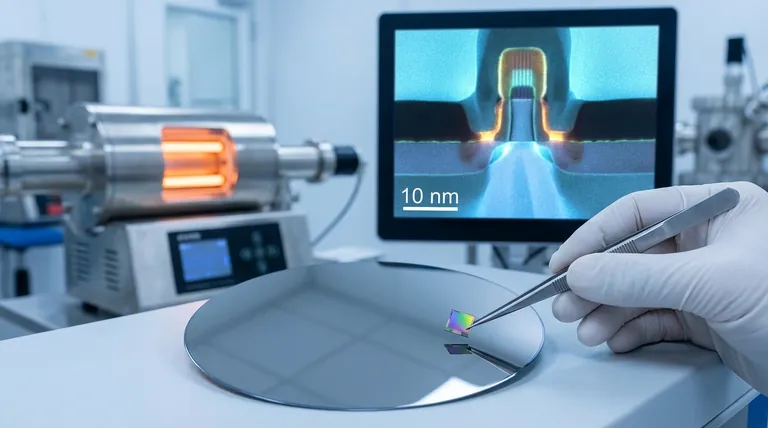

半導体の実際の作業は、ウェハー上に構築されたトランジスタと回路で行われます。これらは、さまざまな材料の信じられないほど薄い膜を堆積およびエッチングすることによって作成されます。

これらのアクティブ層では、「薄い」という言葉では不十分です。その寸法はナノメートル(nm)で測定されます。文脈として、5nm製造プロセスとは、チップ上の特徴がわずか約20個のシリコン原子幅であることを指します。

ダイ:ウェハーの切断

1枚のウェハーには、何百、あるいは何千もの同一の個々の回路が含まれています。ウェハーは、これらの個々の長方形のユニットに正確に切断、つまりダイシングされます。各ユニットはダイと呼ばれます。

1つのダイは、数ミリメートル四方程度の壊れやすい小さなシリコンの薄片で、そのナノメートルスケールの層には数十億個のトランジスタが含まれています。

パッケージング:保護と接続

むき出しのシリコンダイは、直接使用するにはあまりにも壊れやすいです。それは保護用のパッケージに収められます。これは通常、私たちが「チップ」として認識する黒いプラスチックまたはセラミックのコンポーネントです。

このパッケージは2つの重要な役割を果たします。繊細なダイを環境から保護し、チップをより大きな回路基板に接続するために必要な金属ピンまたはパッドを提供します。パッケージはかさばり、厚みを増しますが、半導体自体は内部の薄いダイのままです。

薄さが究極の目標である理由

半導体エンジニアは、チップの機能層をより薄く、より小さくするための絶え間ない競争にいます。この薄さへの執着は、性能に直接結びついています。

速度と効率

トランジスタの速度は、オンオフを切り替える速さによって決まります。より薄く、より小さいトランジスタでは、電子が移動する距離がはるかに短くなります。

これは、短いスプリントが長いランよりも時間とエネルギーを必要としないのと同様に、より速いスイッチング速度とより低い消費電力に直接つながります。

密度とムーアの法則

より薄い層とより小さいコンポーネントにより、エンジニアは同じ物理的領域により多くのトランジスタを詰め込むことができます。この原理はムーアの法則の核心です。

チップあたりのトランジスタ数が増えるということは、同じサイズのデバイス内で、より多くの処理能力、より多くのメモリ、より高度な機能が実現することを意味します。

トレードオフの理解

微細な薄さを追求することは、課題がないわけではありません。性能の向上には、エンジニアリングと物理的な大きなトレードオフが伴います。

製造の複雑さ

ナノメートルスケールの層を製造することは、非常に困難で費用がかかります。「ファブ」として知られる数十億ドル規模の施設と、人類が開発した中で最も精密な製造プロセスが必要です。

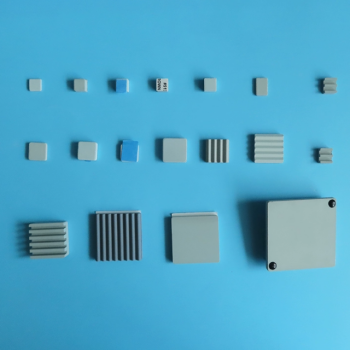

熱放散

個々のトランジスタは小型化されるほど効率的ですが、数十億個を狭い空間に詰め込むと、大規模な熱密度問題が発生します。「薄い」ダイは非常に多くの熱を発生させるため、損傷なく動作させるためには、ヒートシンクやファンなどの「厚い」冷却ソリューションが必要となることがよくあります。

量子リーク

絶縁層がわずか数原子の厚さになると、トンネル効果と呼ばれる量子力学的効果が深刻な問題となります。電子はこれらの極薄の障壁を「漏れ」通過することができ、電力を浪費し、計算エラーを引き起こします。これは、エンジニアが常に戦っている根本的な物理的限界です。

目標に合った選択をする

半導体の厚さに関するあなたの視点は、あなたの役割と達成すべき目標によって全く異なります。

- ハードウェア設計が主な焦点の場合: より小さく、より薄いトランジスタによる性能向上と、熱管理および電力の完全性という重要な必要性とのバランスを取る必要があります。

- ソフトウェア開発が主な焦点の場合: 現代の「薄い」ハードウェアの速度を活用できますが、チップ上の熱放散の物理的限界によって性能が抑制される可能性があることに注意してください。

- ビジネスまたは投資が主な焦点の場合: 「薄さ」の追求(プロセスノードの進歩)を技術進歩の主要な原動力と見なすべきですが、それに伴う莫大な設備投資と物理的障壁を認識してください。

半導体の力がその微細な薄さから生まれることを理解することは、現代のほぼすべてのテクノロジーの基本的な背景を提供します。

まとめ表:

| コンポーネント | 典型的な厚さ | 目的 |

|---|---|---|

| シリコンウェハー | < 1 mm | 構造的な基盤を提供する |

| アクティブ層 | ナノメートル (nm) | 機能回路とトランジスタ |

| ダイ(チップ) | 数 mm(辺長) | 個々の回路ユニット |

| 最終パッケージ | 様々(チップケーシング) | 保護と外部接続 |

KINTEKでラボの精度を解き放つ

薄膜技術の力を活用することは、現代の半導体革新の核心です。KINTEKでは、これらの微細な層の精密な製造と分析をサポートする高品質のラボ機器と消耗品の提供を専門としています。材料研究、半導体開発、またはエレクトロニクス試験に携わっているかどうかにかかわらず、当社のソリューションは、お客様の作業の厳格な要求を満たすように設計されています。

KINTEKを選ぶ理由

- 精密ツール:成膜システムからエッチング装置まで、ナノメートルスケールの層を作成および処理するための信頼性の高いツールを提供します。

- 専門家によるサポート:当社のチームは半導体製造の課題を理解しており、お客様のプロセスを最適化するお手伝いをします。

- オーダーメイドのソリューション:最先端の薄膜アプリケーションを通じて技術を進歩させることに焦点を当てた研究所やR&Dチームにサービスを提供しています。

半導体研究または生産における能力を向上させる準備はできていますか?今すぐお問い合わせください。KINTEKがお客様のラボのニーズをどのようにサポートし、画期的な結果を達成するお手伝いができるかについてご相談ください。

ビジュアルガイド

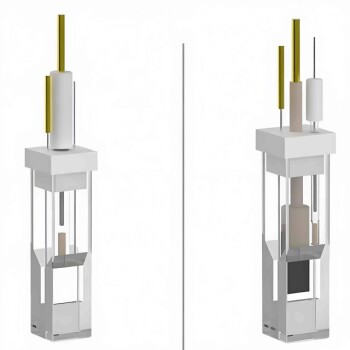

関連製品

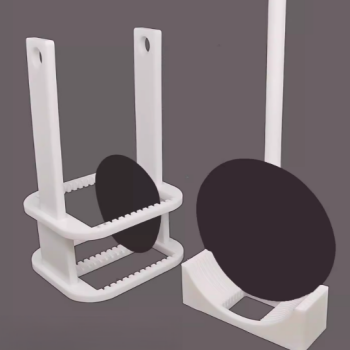

- 半導体およびラボ用途向けのカスタマイズ可能なPTFEウェーハキャリア

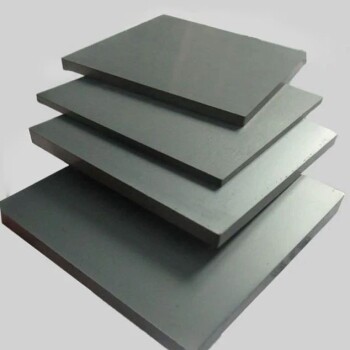

- 窒化ホウ素(BN)セラミックプレート

- 炭化ケイ素(SiC)セラミックシート 耐摩耗性エンジニアリング 高性能ファインセラミックス

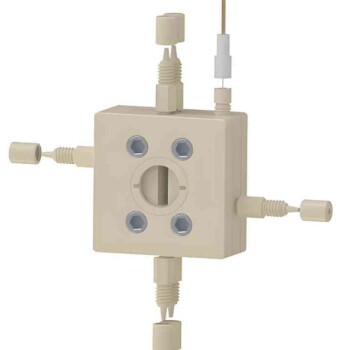

- 薄層分光電気分解セル

- 実験室用参照電極 カロメル 銀塩化水銀 硫酸水銀