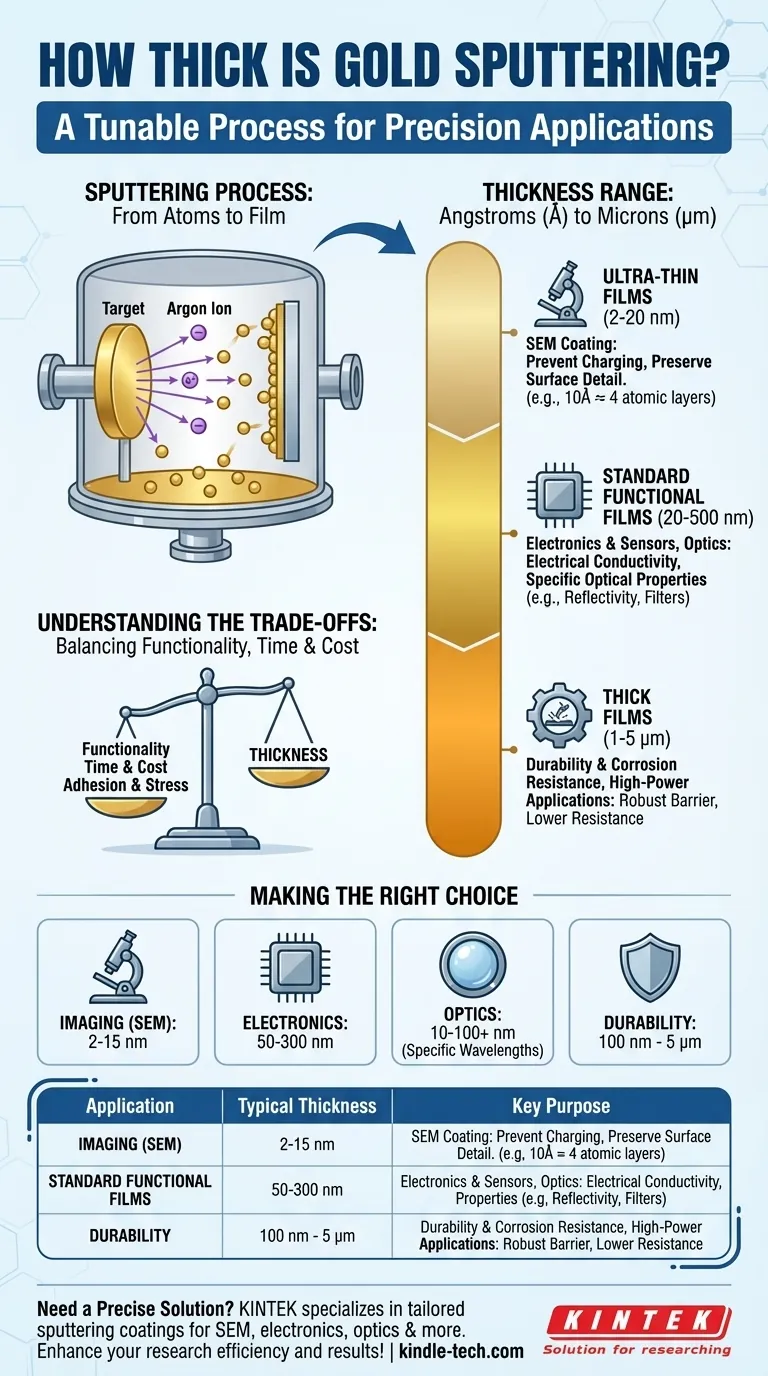

実際には、スパッタリングによって成膜される金層は非常に薄いです。厚さは精密に制御され、通常は数オングストローム(Å)、これはわずか数原子層に相当しますが、数マイクロメートル(μm)に及びます。この広い範囲により、この技術は非常に特定の科学的および産業的用途に適応させることができます。

重要な点は、金のスパッタリングが単一の標準的な厚さではないということです。これは、厚さが主要な変数となる高度に調整可能な成膜プロセスであり、電気伝導性、光学的透明性、またはイメージングのための表面準備など、望ましい結果を達成するために意図的に設計されます。

金のスパッタリングとは?

厚さを理解するためには、まずプロセスを理解する必要があります。金のスパッタリングは、基板上に薄く均一な金属膜を作成するために使用される物理気相成長(PVD)法です。

コアメカニズム

このプロセスは真空チャンバー内で行われます。通常、アルゴンなどの不活性ガスからの高エネルギーイオンが加速され、「ターゲット」と呼ばれる固体の金源に照射されます。このエネルギーによる衝突が、ターゲットから個々の金原子を叩き出し(スパッタリングし)ます。

原子から膜へ

放出されたこれらの金原子は真空を通過し、基板(コーティングされる物体)上に堆積し、原子層ごとに徐々に膜を形成します。その結果、基板の表面に正確に適合する、極めて均一で密度の高いコーティングが得られます。

厚さの範囲を解明する

「オングストロームからマイクロメートル」という範囲は広大です。選択される特定の厚さは、用途に完全に依存します。

オングストロームからナノメートルスケール(超薄膜)

1オングストローム(Å)は1ナノメートル(nm)の10分の1です。10 Å(1 nm)の膜は、わずか約4原子層の厚さしかありません。

これらの超薄膜、通常は2~20 nmの膜は、走査型電子顕微鏡(SEM)用の非導電性サンプルのコーティングとして最も有名に使用されます。この薄い層は、サンプルの表面の詳細を隠すことなく、電子の帯電を防ぐのに十分な厚さです。

ナノメートルスケール(標準的な機能性膜)

これは機能的用途で最も一般的な範囲です。20 nmから500 nmの厚さは、エレクトロニクス、センサー、光学分野で標準的です。

この範囲では、金膜は回路や電極に対して優れた電気伝導性を提供するか、赤外線スペクトルで高い反射率のような特定の光学的特性を提供します。

マイクロメートルスケール(厚膜)

1マイクロメートル(μm)は1,000ナノメートルです。スパッタリングで1~5 μmの厚さに到達することは可能ですが、プロセスが遅く高価であるため、あまり一般的ではありません。

これらのより厚い膜は、より高い耐久性、高出力用途でのより低い電気抵抗、またはより堅牢な耐食性バリアが要求される用途のために予約されています。

トレードオフの理解

スパッタリングの厚さを選択することは、競合する技術的および経済的要因のバランスを取ることを伴います。選択する厚さは常に妥協点となります。

厚さと機能性のトレードオフ

超薄膜の5 nmフィルムは、導電性がありながら電子に対して半透明であるため、SEMには最適であり、表面の詳細を保持します。しかし、その電気抵抗はセンサー電極には高すぎます。

逆に、200 nmの膜は電極として優れた導電性を提供しますが、微小サンプルの微細なディテールを完全に覆い隠してしまいます。

厚さと時間およびコストのトレードオフ

時間と厚さの関係はほぼ線形です。目的の厚さを2倍にすると、プロセス時間と高価な金ターゲットの消費量も約2倍になります。

マイクロメートル厚の膜を得るには数時間かかる場合があり、数分しかかからないナノメートルスケールの膜を堆積させるよりも大幅にコストがかかります。

密着性と応力

膜が厚くなるにつれて、内部応力が蓄積し、密着不良や亀裂につながる可能性があります。これは特にマイクロメートルスケールの膜で顕著であり、基板への密着性を確保するためには慎重なプロセス最適化が必要です。

用途に応じた適切な選択

正しい厚さを選択するには、まず主な目標を定義する必要があります。

- 主な焦点がイメージング(SEM)である場合: 2~15 nmの超薄膜を目指します。表面の特性を隠すことなく帯電を防ぐのに十分な導電性が必要です。

- 主な焦点がエレクトロニクス(電極、接点)である場合: 50~300 nmの範囲は、優れた導電性と合理的なコストおよび処理時間のバランスをとるための一般的な出発点です。

- 主な焦点が光学(ミラー、フィルター)である場合: 厚さは重要であり、必要な反射率または透過率に応じて、10 nmから100 nm超まで、特定の波長に厳密に依存します。

- 主な焦点が耐久性または耐食性である場合: 数百ナノメートルから始まり、低マイクロメートル範囲に及ぶ可能性のある、より厚い膜が必要になるでしょう。

結局のところ、スパッタリングされた金層の厚さは固定値ではなく、特定の科学的または産業的目標の要求を満たすために精密に設計されたパラメータなのです。

要約表:

| 用途 | 標準的な厚さ範囲 | 主な目的 |

|---|---|---|

| SEMコーティング | 2 - 20 nm | 帯電防止、詳細の保持 |

| エレクトロニクスおよびセンサー | 20 - 500 nm | 電気伝導性、電極 |

| 光学(ミラー/フィルター) | 10 - 100+ nm | 特定の反射率/透過率 |

| 耐久性/耐食性 | 100 nm - 5 μm | 堅牢なバリア、低抵抗 |

研究室向けに精密な金のスパッタリングソリューションが必要ですか? KINTEKは、SEM、エレクトロニクス、光学などのためのテーラーメイドのスパッタリングコーティングを提供するラボ機器および消耗品の専門企業です。当社の専門知識により、特定の用途に対して最適な厚さ、密着性、性能が保証され、研究効率と結果が向上します。今すぐお問い合わせいただき、プロジェクトの要件についてご相談ください!

ビジュアルガイド