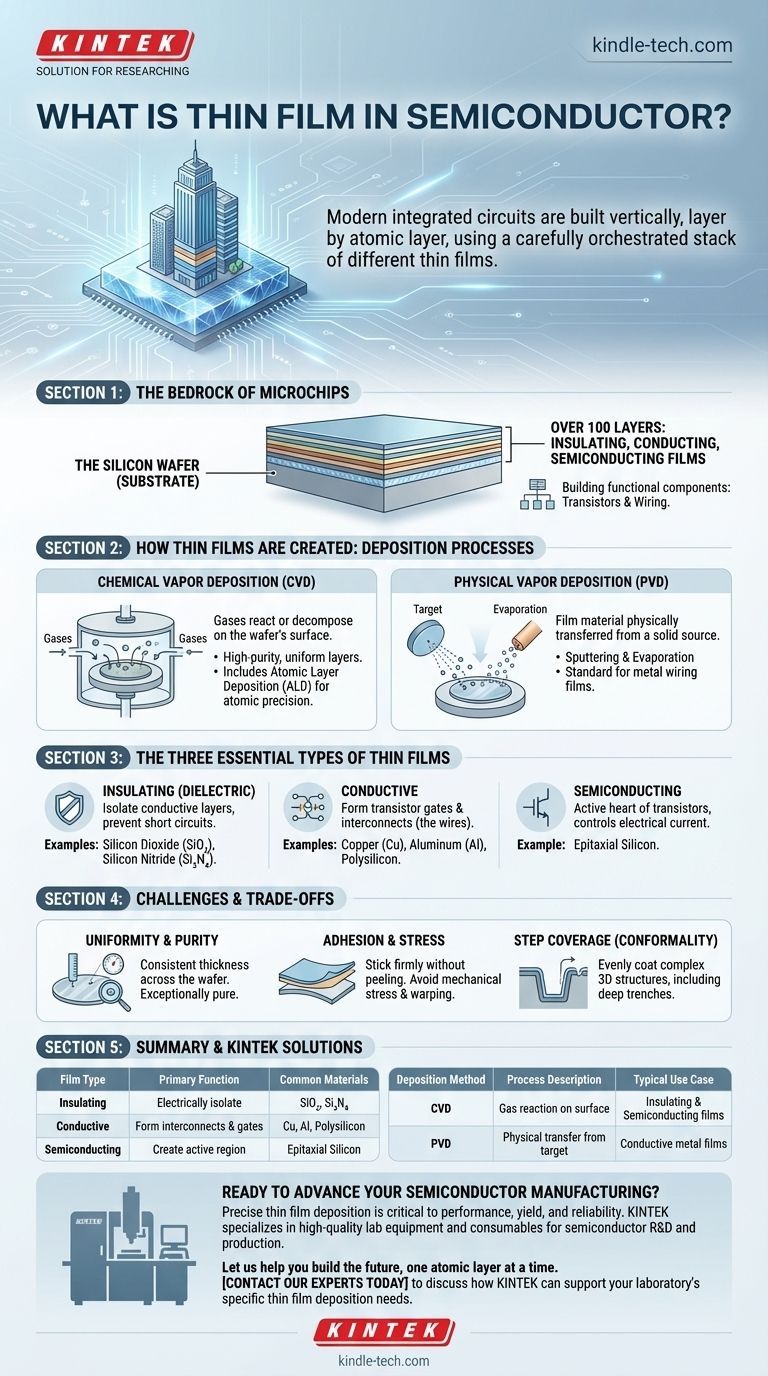

半導体製造において、薄膜とは、数マイクロメートルから1ナノメートル未満の厚さの材料層であり、シリコンウェハー上に意図的に堆積されます。これらの膜は元のシリコン結晶の一部ではなく、マイクロチップの機能部品(トランジスタや配線など)を構築するために、正確な順序で追加されます。

把握すべき核心的な概念は、現代の集積回路がシリコンのブロックから削り出されるのではなく、導体、絶縁体、活性半導体領域として機能する異なる薄膜の注意深く編成された積層体を使用して、原子層ごとに垂直に構築されるということです。

薄膜がマイクロチップの基盤である理由

マイクロチップの構築を、シリコン基盤の上に高層ビルを建てるようなものだと考えてみてください。薄膜は、この構造のあらゆる部分にとって不可欠な建築材料です。

ウェハー上に堆積される各層には、特定の電気的または構造的な目的があります。これらの膜を堆積し、その後パターン化することで、エンジニアは数十億個のトランジスタとそれらを接続する複雑な配線ネットワークを形成する、複雑な三次元アーキテクチャを作り出します。

基盤:シリコンウェハー

プロセス全体は、高純度の結晶シリコンウェハーから始まります。このウェハーは、その後のすべての薄膜層が構築される基板、つまり基本的な基層として機能します。

構成要素:層の上に層を重ねる

完成したマイクロプロセッサは、100以上の異なる材料層を持つことがあります。この積層体は、絶縁性、導電性、半導体性の薄膜の繰り返しシーケンスで構成されており、それぞれが最終的な回路に貢献しています。

薄膜の作成方法:成膜プロセス

薄膜をウェハーに塗布するプロセスは成膜として知られています。成膜技術には2つの主要なファミリーがあり、それぞれ異なる種類の膜の作成に適しています。

化学気相成長(CVD)

CVDでは、ウェハーをチャンバーに入れ、1つ以上の揮発性ガスにさらします。これらのガスはウェハー表面で反応または分解し、固体材料である薄膜を残します。

この方法は非常に汎用性が高く、化学反応によって非常に高純度で均一な層が生成されるため、絶縁膜や半導体膜の作成に使用されます。主要なバリアントである原子層堆積(ALD)は、一度に単一の原子層を構築することを可能にし、比類のない精度を提供します。

物理気相成長(PVD)

PVDでは、膜材料は固体源(「ターゲット」)として始まります。この材料は、化学反応なしに物理的にウェハー上に転送されます。

PVDの主な2つの方法は、高エネルギーイオンがターゲットを衝突させて原子を叩き出すスパッタリングと、ターゲットを加熱して蒸発させる蒸着です。PVDは、回路の配線として機能する金属膜を堆積するための標準的な方法です。

薄膜の3つの必須タイプ

機能的に、半導体デバイス内のすべての膜は、3つのカテゴリのいずれかに分類されます。

絶縁(誘電体)膜

これらの膜は電気を伝導しません。その主な役割は、導電層を互いに絶縁し、短絡を防ぐことです。二酸化ケイ素(SiO₂)と窒化ケイ素(Si₃N₄)が最も一般的な例です。

導電膜

これらの膜はチップの「配線」であり、トランジスタのゲートや、それらの間で信号を伝達する相互接続を形成します。材料には、銅(Cu)、タングステン(W)、アルミニウム(Al)などの金属や、高濃度にドープされたポリシリコンが含まれます。

半導体膜

これらの膜はトランジスタの活性な心臓部であり、電流が実際に制御される場所です。最も重要な例はエピタキシャルシリコンであり、ウェハー上に成長させた単結晶シリコンの層で、純粋な品質と正確に制御された電気的特性を持っています。

トレードオフと課題の理解

完璧な薄膜を堆積させることは、非常に大きな技術的課題です。これらの層の品質は、最終的なチップの性能、消費電力、信頼性に直接影響します。

均一性と純度

膜は、300mmウェハー全体で一貫した厚さを持つ必要があります。わずかなばらつきでも、チップのある領域のトランジスタが別の領域のトランジスタとは異なる動作をする可能性があります。また、膜は非常に純粋でなければならず、たった1つの異質な原子でもデバイスを台無しにする可能性があります。

密着性と応力

堆積された膜は、剥がれたり層間剥離したりすることなく、その下の層にしっかりと密着する必要があります。さらに、成膜プロセスは機械的応力を生じさせることがあり、これによりウェハーが物理的に反ったり、その上に構築された繊細な構造が損傷したりする可能性があります。

段差被覆性(コンフォーマリティ)

チップがより三次元的になるにつれて、膜は深く狭いトレンチの側面と底面を均一に覆うことができる必要があります。上部が厚く側面が薄い膜は「段差被覆性」が悪く、故障の原因となる可能性があります。

薄膜と目標の関連付け

特定の薄膜技術の重要性は、エンジニアリングの目標に完全に依存します。

- トランジスタ性能が主な焦点の場合:極薄のゲート誘電体とエピタキシャルシリコン半導体膜の純度が最重要です。

- チップ速度が主な焦点の場合:相互接続用の低抵抗導電膜(銅など)と、それらを絶縁するための低誘電率誘電体膜の成膜を習得することが鍵となります。

- 製造歩留まりが主な焦点の場合:すべてのウェハーで膜の絶対的な均一性、純度、コンフォーマリティを確保するために、成膜プロセスを完璧にすることが目標です。

最終的に、薄膜の作成と制御の科学を習得することが、現代のエレクトロニクスを進歩させるための基本的な要件です。

要約表:

| 膜の種類 | 主な機能 | 一般的な材料 |

|---|---|---|

| 絶縁(誘電体) | 導電層を電気的に絶縁する | 二酸化ケイ素(SiO₂)、窒化ケイ素(Si₃N₄) |

| 導電性 | トランジスタのゲートと相互接続(配線)を形成する | 銅(Cu)、アルミニウム(Al)、ポリシリコン |

| 半導体性 | トランジスタの活性領域を作成する | エピタキシャルシリコン |

| 成膜方法 | プロセス説明 | 典型的な使用例 |

| 化学気相成長(CVD) | ウェハー表面でガスが反応して固体膜を形成する | 高純度絶縁膜および半導体膜 |

| 物理気相成長(PVD) | 固体ターゲット材料が物理的にウェハーに転送される | 配線用の導電性金属膜 |

半導体製造を進化させる準備はできていますか?

薄膜の精密な堆積は、チップの性能、歩留まり、信頼性にとって極めて重要です。KINTEKは、半導体の研究開発および生産向けに高品質の実験装置と消耗品を提供することを専門としています。CVDシステムによる完璧な均一性の達成に焦点を当てる場合でも、PVDによる低抵抗金属の堆積に焦点を当てる場合でも、当社のソリューションは現代の半導体製造の厳しい要求を満たすように設計されています。

KINTEKがお客様のラボの特定の薄膜堆積ニーズをどのようにサポートできるか、今すぐ専門家にお問い合わせください。原子層ごとに未来を築くお手伝いをいたします。

ビジュアルガイド